Desbloquear el código de nomenclatura RISC-V

La arquitectura de conjunto de instrucciones (ISA) RISC-V brinda una oportunidad única. Su estructura permite a los desarrolladores utilizar procesadores con una amplia gama de tamaños y rendimiento que ofrecen una compatibilidad de software sin precedentes. La clave para aprovechar esta compatibilidad es comprender el código de nomenclatura del núcleo RISC-V.

A diferencia de la mayoría de las arquitecturas de procesadores, RISC-V es de código abierto y está disponible para los desarrolladores sin derechos de licencia ni derechos de regalía. Además, la ISA está diseñada para ser flexible, lo que permite a los desarrolladores elegir qué bloques de instrucciones desean implementar y omitir lo que no necesitan, incluso agregando instrucciones personalizadas si lo desean. La intención es estimular el desarrollo de múltiples núcleos de procesador con diferentes atributos de tamaño y rendimiento que comparten una base común.

Esta base común proporciona un alto nivel de compatibilidad de software entre procesadores independientemente de sus conjuntos de características. El código para un procesador RISC-V mínimo que implemente solo el conjunto de instrucciones de números enteros, por ejemplo, se ejecutará sin modificaciones en un procesador más potente que tenga capacidad tanto de números enteros como de punto flotante. El código que usa las instrucciones de punto flotante no se ejecutará, por supuesto, en la máquina de solo enteros, pero tampoco hará que el procesador se bloquee. Las instrucciones no implementadas simplemente generarán una trampa de instrucción ilegal.

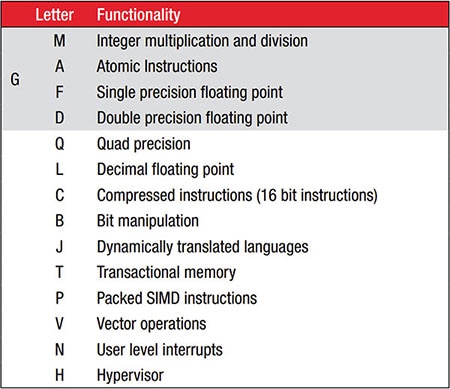

La ISA RISC-V logra esta flexibilidad al dividir sus instrucciones en grupos esencialmente independientes que tienen códigos de máquina que no se superponen. Estos grupos de instrucciones se denominan “extensiones estándar”, y la ISA ha definido numerosas extensiones estándar que proporcionan la mayoría de las funciones que los desarrolladores pueden necesitar. Cada extensión estándar se identifica con un código de letra. La extensión estándar “M”, por ejemplo, proporciona instrucciones para multiplicar o dividir dos números enteros contenidos en registros De manera similar, la extensión estándar “F” proporciona instrucciones para operaciones de punto flotante de precisión simple.

Debido a que los desarrolladores de procesadores pueden combinar extensiones estándar al implementar un núcleo RISC-V, podría parecer que los usuarios necesitarían leer las hojas de especificaciones y los manuales de programación con atención para determinar qué puede hacer realmente el procesador para el que pretenden diseñar. Pero hay una solución más sencilla. RISC-V utiliza una convención de numeración de núcleo que informa inmediatamente a los usuarios de las capacidades del núcleo.

La convención de numeración comienza con la especificación básica. RISC-V ha definido cuatro especificaciones básicas:

- RV32I tiene un conjunto de instrucciones de enteros de 32 bits y ofrece 32 registros de propósito general

- RV32E utiliza un conjunto de instrucciones de 32 bits dirigido a aplicaciones integradas con 16 registros

- RV64I tiene un conjunto de instrucciones de enteros de 64 bits con 32 registros

- RV128I tiene un conjunto de instrucciones de enteros de 128 bits con 32 registros

Estas especificaciones básicas definen un procesador completamente funcional, aunque básico. La mayoría de los desarrolladores, sin embargo, optarán por agregar una o más extensiones de conjuntos de instrucciones estándar a su diseño. Estas extensiones estándar y sus letras de identificación se enumeran en la Figura 1.

Figura 1: Las extensiones del conjunto de instrucciones estándar para los procesadores RISC-V utilizan códigos de letras para indicar su presencia en la convención de numeración de un núcleo. (Fuente de la imagen: DigiKey)

Figura 1: Las extensiones del conjunto de instrucciones estándar para los procesadores RISC-V utilizan códigos de letras para indicar su presencia en la convención de numeración de un núcleo. (Fuente de la imagen: DigiKey)

Una designación de núcleo RISC-V completa proporciona la especificación base adjunta con las letras de las extensiones estándar que implementa, en el orden indicado en la Figura 1. Un pequeño sistema en chip (SoC) que utiliza recursos mínimos, entonces, podría tener la designación RV32EMAB. Esto significa que el núcleo implementa el conjunto de instrucciones de enteros de 32 bits para dispositivos integrados, tiene 16 registros y ejecuta la multiplicación y división de números enteros, así como las instrucciones atómicas. No tiene matemáticas de punto flotante, pero admite la manipulación de bits.

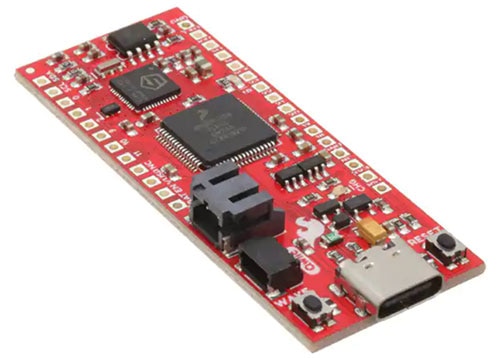

Por lo tanto, al elegir un chip RISC-V para su diseño, los usuarios solo necesitan mirar la designación del núcleo para comprender qué funcionalidad proporciona. Por ejemplo, el procesador en la placa de evaluación DEV-15799 FE310 Thing Plus RISC-V de SparkFun Electronics aparece como un núcleo RV32IMAC (Figura 2).

Figura 2: El procesador RISC-V de la placa DEV-15799 se llama RV32IMAC, lo que significa, entre otras características, que tiene un conjunto de instrucciones de enteros de 32 bits, 32 registros y ofrece instrucciones atómicas. (Fuente de la imagen: SparkFun Electronics)

Figura 2: El procesador RISC-V de la placa DEV-15799 se llama RV32IMAC, lo que significa, entre otras características, que tiene un conjunto de instrucciones de enteros de 32 bits, 32 registros y ofrece instrucciones atómicas. (Fuente de la imagen: SparkFun Electronics)

Esto significa que tiene un conjunto de instrucciones de enteros de 32 bits, 32 registros, implementa la multiplicación y división de números enteros, ofrece instrucciones atómicas y admite instrucciones comprimidas (16 bits) para minimizar el espacio de código. Cualquier código desarrollado en esta placa también podrá ejecutarse en cualquier otro núcleo RV32I con las extensiones estándar de multiplicar y acumular (MAC).

En otro ejemplo, el módulo SoC 114991684 Sipeed MAXIX-I RISC-V de Seeed Technology enumera su núcleo RISC-V como RV64IMAFDC. Tiene un conjunto de instrucciones de 64 bits con multiplicar y dividir enteros, instrucciones atómicas, punto flotante de precisión simple y doble e instrucciones comprimidas. El código desarrollado para este procesador debería poder ejecutarse en cualquier procesador RISC-V con las mismas designaciones de núcleo, aunque es posible que sea necesario ajustar la asignación de memoria de los periféricos y demás.

Conclusión

Con el código de nomenclatura RISC-V en la mano, los usuarios están bien posicionados para comenzar a experimentar con confianza con esta poderosa arquitectura. Al hacer coincidir los códigos de núcleo, los usuarios pueden estar seguros de que sus esfuerzos de programación con un procesador serán altamente portables a otros procesadores RISC-V.

Un buen lugar para comenzar esta experimentación podría ser consultar la Guía de RISC-V, que describe la configuración inicial y el uso de varias placas de evaluación RISC-V diferentes.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum