Cómo la extensión atómica RISC-V le brinda capacidades superiores de manipulación de bits

La tasa de adopción de la arquitectura RISC-V (computación por conjunto de instrucciones reducidas) está aumentando rápidamente y, por un buen motivo, su influencia en la industria es cada vez mayor.

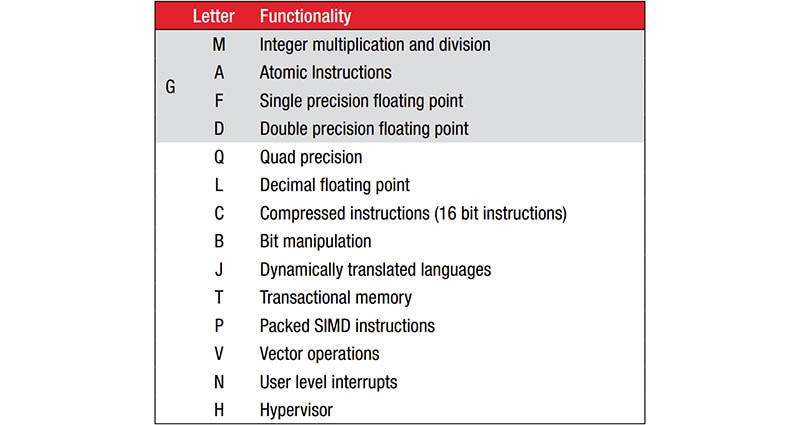

Además de la arquitectura central y su verdadera ISA (arquitectura de conjunto de instrucciones) reducidas, se ve reforzada por una serie de extensiones estandarizadas (Figura 1). Por ejemplo, un núcleo RISC-V de 32 bits (RV32) que admita el punto flotante de precisión simple y también las instrucciones comprimidas se denominaría RV32FC, según la lista de extensiones que se muestra.

Figura 1: La ISA RISC-V mejora gracias a una serie de extensiones de instrucciones estandarizadas, que se indica con un sufijo de letra después del nombre del núcleo. (Fuente de la imagen: RISC-V.org)

Figura 1: La ISA RISC-V mejora gracias a una serie de extensiones de instrucciones estandarizadas, que se indica con un sufijo de letra después del nombre del núcleo. (Fuente de la imagen: RISC-V.org)

Para muchas aplicaciones de IA (inteligencia artificial) y ML (aprendizaje automático), así como también para los sistemas integrados avanzados, las cuatro extensiones más necesarias son: M (multiplicación y división de enteros), A (instrucciones atómicas), F (punto flotante de precisión simple) y D (punto flotante de precisión doble). Sin embargo, en lugar de designar un núcleo como en RV32MAFD, todas estas se agrupan juntas bajo el sufijo G, como en RV32G.

Para obtener más información sobre las diversas extensiones y la RISC-V en general, consulte el libro electrónico de RISC-V de DigiKey disponible en el sitio de EDU.

Personalmente, dado que mi experiencia inicial con procesadores fue en sistemas integrados profundos, suelo examinar detenidamente el soporte de manipulación de bits de lectura-modificación-escritura de una arquitectura en la memoria de datos. Para estas aplicaciones, es muy común establecer y borrar bits de registros periféricos y semáforos. Sin instrucciones sobre la manipulación nativa de bits, un núcleo necesitaría copiar el contenido de las ubicaciones de la memoria de datos en un registro central; establecer, borrar o alternar los bits usando las instrucciones OR, AND o XOR respectivamente; y luego almacenar el resultado de nuevo en la ubicación de la memoria de datos. Esto no solo requiere tiempo adicional, sino que, en algunos casos, he visto el código inflado hasta en un 20% para algunas aplicaciones de control integradas.

En algunas aplicaciones, el código inflado y la disminución del rendimiento pueden ser aceptables. Sin embargo, mientras se procesan estas tres instrucciones, una interrupción puede eliminar bruscamente el control del programa de la operación, o peor aún, en un sistema multiprocesador, otro núcleo podría leer desde esa misma ubicación de memoria. Deshabilitar las interrupciones o bloquear la memoria para garantizar que estos eventos no dañen la memoria de datos requiere complicaciones e instrucciones adicionales que pueden generar problemas de rendimiento.

Arm intentó resolver estos problemas implementando bandas de bits, que funcionan para operaciones con bits simples. Sin embargo, en mi opinión, RISC-V ha implementado una solución más elegante y flexible.

Motivos por los que la extensión atómica es tan elegante

La extensión RISC-V A (atómica) admite dos operaciones, una instrucción de carga reservada/almacenamiento condicional, que no se analizará aquí, y una instrucción binaria/de operación bit a bit que ofrece una manipulación de bits simple en la memoria de datos. Si bien la extensión RISC-V B de manipulación de bits admite una serie de instrucciones de control de bits complejas, la extensión atómica no solo está dirigida a sistemas multiprocesador. También ayuda en sistemas integrados más pequeños, donde los requisitos de manipulación de bits necesarios son más simples. Un ejemplo de dicho sistema es el módulo RISC-V de 64 bits y doble núcleo 114991684 de Seeed Technology. Tiene dos núcleos RV64GC que deben trabajar juntos y funcionar bien con su SRAM (memoria estática de acceso aleatorio) de datos compartidos.

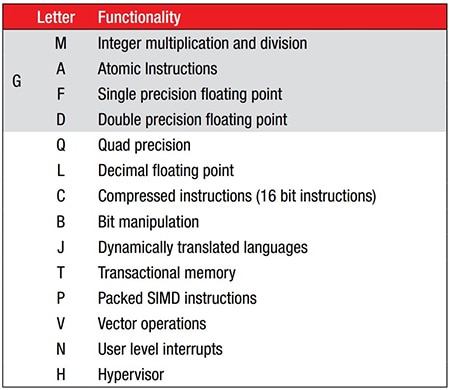

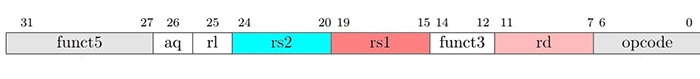

El formato de la AMO (operación de memoria atómica) de la extensión A de RISC-V se muestra en la Figura 2.

Figura 2: El formato de instrucción de la AMO de RISC-V admite operaciones binarias atómicas en la memoria de datos con una sola instrucción. (Fuente de la imagen: RISC-V.org (mejorado por [Bill Giovino])

Figura 2: El formato de instrucción de la AMO de RISC-V admite operaciones binarias atómicas en la memoria de datos con una sola instrucción. (Fuente de la imagen: RISC-V.org (mejorado por [Bill Giovino])

La AMO es una poderosa instrucción de lectura-modificación-escritura que admite varias operaciones binarias directamente en la memoria de datos señalada en rs1 con una sola instrucción. Con referencia a la Figura 2, la operación carga el contenido de la ubicación de la dirección de la memoria de datos en rs1 y almacena el valor en el registro rd. Luego realiza una operación binaria sobre el valor de rd con el valor en rs2 y guarda ese resultado en rd y nuevamente en la ubicación de la dirección de la memoria de datos en rs1.

Las operaciones bit a bit admitidas son OR (conjunto de bits), AND (borrado de bits) y XOR (alternancia de bits). Esto permite la manipulación atómica de uno o más bits directamente en la memoria de datos. Esto también evita conflictos de memoria si los dos núcleos RV64GC están usando la misma dirección de memoria al mismo tiempo. Esto es muy útil en las pequeñas aplicaciones integradas a la hora de configurar registros periféricos en la memoria, así como para simplificar las operaciones de semáforo.

Las operaciones adicionales que admite la AMO de RISC-V son el máximo de enteros, el mínimo de enteros y el intercambio. La ADD (adición) binaria también es compatible, lo cual permite la adición binaria directa, incluyendo el incremento directo de un contador en la memoria de datos.

El núcleo RV64 admite operaciones de 32 y 64 bits. Para la manipulación de bits con el RV64, es importante que solo opere con datos de 64 bits, ya que la operación firmará y extenderá los datos de 32 bits ubicados en rd.

Conclusión

La ISA de RISC-V es la primera competidora seria que viene a desafiar a la ISA de Arm. Sus extensiones de la ISA ofrecen un método estandarizado para mejorar el núcleo con instrucciones que pueden mejorar de manera rentable el rendimiento de una aplicación. Estoy especialmente entusiasmado con la extensión atómica opcional.

Si bien es útil y casi necesaria para sistemas multiprocesador, la extensión atómica también es una forma eficiente de brindar control de manipulación de bits directamente a la memoria de datos. Esto ofrece una ventaja significativa sobre muchas arquitecturas existentes reduciendo el tamaño del código y mejorando el rendimiento.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum