Use LDO ajustables de baja fuga para extender la duración de la batería en diseños portátiles

Colaboración de Editores de DigiKey de América del Norte

2019-11-06

Los reguladores de voltaje de conmutación tienen una reputación de alta eficiencia, lo que los convierte en una opción popular en los diseños de fuentes de alimentación de dispositivos portátiles para extender la duración de la batería. Sin embargo, estos reguladores pueden ser eléctricamente ruidosos, ocupan mucho espacio, y son complejos de diseñar y relativamente caros.

En comparación, los reguladores lineales proporcionan una salida libre de ondulación y son simples, compactos y económicos. Sin embargo, en un amplio rango de carga, generalmente son menos eficientes que los reguladores de conmutación, lo que afecta la duración de la batería. De todas formas, al emplear un regulador lineal de (LDO), a menudo denominado simplemente “LDO”, y optimizar la salida del dispositivo para garantizar que funcione en la región más eficiente, los ingenieros pueden acercarse a la eficiencia general de un regulador de conmutación.

Sin embargo, sigue existiendo un problema clave: los dispositivos portátiles cuentan con un diseño que les permite pasar mucho tiempo en modo de espera de bajo consumo para que la duración de la batería no se vea afectada. Incluso en estos modos, el LDO causa un consumo de corriente interno perceptible. Este consumo de corriente, aunque es pequeño, reduce la duración de la batería del producto final.

Una nueva generación de soluciones de LDO aborda el problema. Al usar estos dispositivos, los ingenieros pueden ajustar la corriente de salida y el voltaje de caída para minimizar la disipación de potencia interna cuando el dispositivo portátil está en modo de bajo consumo.

Este artículo muestra cómo seleccionar un LDO para alimentar un dispositivo portátil. Luego explica cómo se puede utilizar una nueva generación de LDO para maximizar la eficiencia sin comprometer la experiencia del usuario.

¿LDO o regulador de conmutación?

Una decisión clave en el proceso de diseño de una fuente de alimentación portátil es la elección del regulador. El ingeniero se enfrenta a tener que elegir entre un regulador de conmutación o un LDO. Cada uno tiene ventajas y desventajas, lo que puede hacer que sea difícil decidir cuál usar para una aplicación en particular (veaComprender las ventajas y desventajas de los reguladores lineales).

Los dispositivos portátiles conllevan una serie de desafíos de diseño que hacen que el proceso de selección sea aún más difícil:

- El uso de pequeñas baterías para colaborar con que el diseño sea compacto

- El requerimiento de una batería de larga duración

- La necesidad de un suministro estable para alimentar una tecnología electrónica sensible

- La capacidad de salir rápidamente de un estado de suspensión para mejorar la experiencia del usuario

Un regulador de conmutación eficiente puede abordar la necesidad de duración de la batería, pero una desventaja importante es el nivel relativamente alto de EMI (interferencia electromagnética) causada por la operación de alta frecuencia del regulador, que podría alterar el microcontrolador y el transceptor sensible del dispositivo portátil.

Este problema se puede resolver mediante el uso de un regulador de conmutación para la conversión de voltaje y la adición de un LDO en serie para minimizar el voltaje y la fluctuación de corriente de la salida del dispositivo. Sin embargo, dicha topología agrega complejidad y costo, y aumenta el tamaño de la fuente de alimentación.

Un enfoque alternativo es utilizar un LDO para un suministro de voltaje estable y maximizar la eficiencia eligiendo un dispositivo de baja disipación de potencia interna y minimizando la diferencia entre los voltajes de entrada y salida del regulador.

Cálculo de eficiencia de un LDO

Lo que determina la eficiencia de un LDO es su corriente de tierra (IGND) y los voltajes de entrada y salida (VIN y VOUT). La fórmula para calcular la eficiencia es:

Eficiencia = IOUT/(IOUT + IGND) × VOUT/VIN × 100%

IGND es la corriente requerida para operar los circuitos internos del LDO (que es la diferencia entre las corrientes de entrada y salida). Una parte clave de esto es la corriente de reposo del LDO (IQ), que alimenta los circuitos internos del LDO cuando la corriente de carga externa es cercana a cero. Incluye la corriente de funcionamiento del amplificador de error, el divisor de voltaje de salida y los circuitos de detección de sobrecorriente y temperatura.

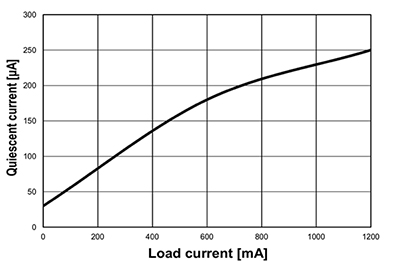

Debido a su impacto en la eficiencia, IGND e IQ son especificaciones clave de la hoja de datos de un LDO. Por ejemplo, un producto adecuado para alimentar un dispositivo portátil, como el LDOMCP1811BT-028/OT de Microchip, tiene cifras de IGND = 180 microamperios (µA) (a IOUT = 300 miliamperios [mA]) y IQ = 250 nanoamperios (nA). La IQ (y, por lo tanto, la IGND) aumenta a medida que aumenta la IOUT. Esta relación se muestra claramente en el LDL112 de STMicroelectronics (Figura 1).

Figura 1: Este gráfico muestra claramente la relación entre la corriente de carga y la corriente de reposo del LDO LDL112 de STMicroelectronics. (Fuente de la imagen: STMicroelectronics)

Figura 1: Este gráfico muestra claramente la relación entre la corriente de carga y la corriente de reposo del LDO LDL112 de STMicroelectronics. (Fuente de la imagen: STMicroelectronics)

Para un LDO que cumple con las cargas típicas de un dispositivo portátil que registra y transmite datos (por ejemplo, varios cientos de miliamperios), la IGND es relativamente insignificante en comparación con la IOUT, por lo que el factor clave que determina la eficiencia se convierte en la diferencia de voltaje que hay entre la entrada y la salida.

Por ejemplo, la eficiencia de un LDO con un VIN de 5 voltios y un VOUT de 3.3 voltios es de un 66%. Sin embargo, la eficiencia aumenta hasta un 91.7% cuando el suministro se reduce a 3.6 voltios. El consumo de energía del LDO se puede calcular a partir de P = (VIN - VOUT) x IOUT.

Sin embargo, minimizar la diferencia entre el voltaje de entrada y de salida para aumentar la eficiencia de un LDO solo puede realizarse hasta cierto punto porque hay un umbral por debajo del cual el dispositivo no puede regular adecuadamente el voltaje de salida. Este umbral mínimo se conoce como voltaje de caída (VDROPOUT). En un dispositivo moderno como el LDL112 de STMicroelectronics, el VDROPOUT mide 350 milivoltios (a 3.3 voltios, salida de 1 A).

Es importante que el diseñador note que el VDROPOUT es el punto en el que el LDO ya no es capaz de regular el voltaje de suministro. Para cumplir con su especificación completa, el LDO suele requerir un “voltaje de margen de sobrecarga” adicional que generalmente agrega otros 250 a 500 mV al VDROPOUT, aunque en el caso de algunos LDO puede llegar hasta 1.5 voltios. El VDROPOUT y el voltaje de margen de sobrecarga deben tenerse en cuenta para determinar la diferencia entre los voltajes de entrada y salida.

Para obtener más información sobre el diseño de un LDO en dispositivos alimentados por batería, consulte Uso de LDO avanzados para cumplir con los desafíos de diseño de la fuente de suministro del sensor inalámbrico de IoT.

Optimización del rendimiento de LDO

Como se demostró anteriormente, en un diseño con restricción de energía, es una buena práctica de ingeniería minimizar la diferencia de voltaje en el LDO, ya que el ahorro de energía resultante puede extender drásticamente la duración de la batería. Sin embargo, hay mucho para hacer cuando el presupuesto de potencia disponible es muy limitado.

Un aspecto a tener en cuenta es el consumo de potencia que se produce cuando un dispositivo portátil está en modo de bajo consumo o de “suspensión”, como cuando el dispositivo no utiliza la capacidad del microcontrolador, transceptor o GPS. Si bien el consumo de corriente del producto final será bajo en ese modo, el LDO debe permanecer activo para minimizar la latencia en el caso de que el usuario presione un botón operativo o active una pantalla táctil.

Cuando el dispositivo portátil está en modo de suspensión, la IOUT es pequeña; en consecuencia, la IGND tiene un mayor efecto sobre la eficiencia que durante el funcionamiento normal. Debido a que la carga en el dispositivo es baja, el consumo de potencia real no es grande; sin embargo, sí es continuo, por lo que durante un período prolongado tendrá un gran impacto en la duración de la batería. Es una buena práctica de diseño elegir un LDO que cumpla con las especificaciones a la vez que ofrezca el menor consumo de corriente interna para minimizar las pérdidas cuando la IOUT es baja.

Mejor aún, la mayoría de los LDO modernos ofrecen una opción para poner el dispositivo en modo apagado llevando a bajo un pin seleccionado. Como resultado, se desconecta el dispositivo completamente de la carga, por lo que se limita efectivamente la IOUT a solo la IGND.

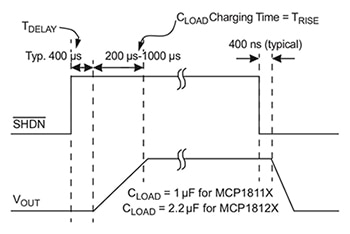

Por ejemplo, el MCP1811A de Microchip incorpora una entrada de SHDN (apagado) que se usa para apagar y encender el voltaje de salida del LDO (Figura 2). El dispositivo funciona con una entrada de 1.8 a 5.5 voltios y ofrece una opción de nueve salidas fijas en un rango de 1 a 4 voltios. El LDO tiene un VDROPOUT de 400 mV, proporciona una salida máxima de hasta 150 mA y presenta una IQ de 250 nA y una IGND de 80 µA (a IOUT = 150 mA, VIN = 5 voltios, VOUT = 4 voltios).

Figura 2: El MCP1811A de Microchip presenta un modo de apagado. El tiempo de respuesta al pin SHDN que sube y la entrega del voltaje regulado varía entre 600 y 1400 µs. (Fuente de la imagen: Microchip Technology)

Figura 2: El MCP1811A de Microchip presenta un modo de apagado. El tiempo de respuesta al pin SHDN que sube y la entrega del voltaje regulado varía entre 600 y 1400 µs. (Fuente de la imagen: Microchip Technology)

Cuando la entrada SHDN es alta (mínimo 70% del VIN), se habilita el voltaje de salida del LDO y el dispositivo suministra el voltaje regulado. Cuando la entrada SHDN se pone bajo (máximo 20% del VIN), el suministro de voltaje regulado se desconecta y el LDO entra en un estado de apagado por baja corriente en la que la IQ típica es de 10 nA y la IGND es de alrededor de 2 µA.

La ventaja de poder poner el MCP1181A en modo apagado es el evidente ahorro de energía, pero la desventaja es el efecto que tiene el tiempo de inicio en la respuesta del sistema. Para asegurarse de que el LDO no se encienda debido a picos de ruido del sistema en el pin SHDN y desperdicie energía de la batería, el circuito de apagado presenta un retraso de 400 microsegundos (μs) en el borde ascendente de la entrada SHDN antes de encender el regulador. Esta es una buena idea desde una perspectiva operativa, pero tiene un impacto en la respuesta. Después del retraso predeterminado, si la entrada SHDN permanece alta, el regulador comienza a cargar el condensador de carga a medida que la salida aumenta de 0 voltios a su valor final regulado. Por lo tanto, el tiempo total desde el encendido de la entrada SHDN hasta la salida que entrega el voltaje de regulación es la suma del tiempo de retraso incorporado de 400 μs y el tiempo de aumento del voltaje de salida. Este tiempo de aumento depende del VOUT y puede variar entre 200 y 1000 μs.

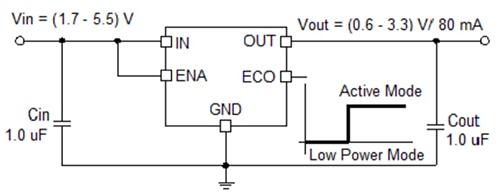

Del mismo modo, el paquete LDO XDFN4 de modo dual NCP171 de ON Semiconductor puede ponerse en modo de apagado al hacer que su pin ENA sea bajo (menos de 0.4 voltios). El LDO tiene un rango de voltaje de salida fijo de 0.6 a 3.3 voltios desde una entrada de 1.7 a 5.5 voltios, y un VDROPOUT de 110 mV. Sin embargo, el NCP171 ofrece un sistema más sofisticado para extender la vida útil de la batería que ayuda a mejorar la respuesta cuando desde un modo de bajo consumo se cambia a la salida de voltaje regulada que se requiere para un funcionamiento normal.

En modo activo, el LDO es capaz de suministrar hasta 80 mA, pero cuando se utiliza el modo de bajo consumo, el voltaje de salida regulado del LDO no se desconecta; en cambio, la IOUT está limitada a un máximo de 5 mA. Debido a que se usa una parte diferente del LDO para la regulación, la IGND se reduce significativamente, lo que extiende la vida útil de la batería. Los modos de bajo consumo (y activo) se pueden seleccionar a través del pin ECO del LDO (Figura 3).

Figura 3: El NCP171 de ON Semiconductor se puede cambiar de un modo activo a uno de bajo consumo a través del pin ECO. En el modo de bajo consumo, la IOUT se limita a un máximo de 5 mA, mientras que la IGND se reduce significativamente. (Fuente de la imagen: ON Semiconductor)

Figura 3: El NCP171 de ON Semiconductor se puede cambiar de un modo activo a uno de bajo consumo a través del pin ECO. En el modo de bajo consumo, la IOUT se limita a un máximo de 5 mA, mientras que la IGND se reduce significativamente. (Fuente de la imagen: ON Semiconductor)

Cuando el pin ECO se lleva a bajo (a tierra), el LDO cambia al modo de bajo consumo. La IQ se reduce de 55 µA a 50 nA. El impacto en la IGND es igualmente significativa: en modo activo, IGND = 420 µA (IOUT = 80 mA), en comparación con el modo de bajo consumo, en el que IGND = 2.5 µA (IOUT = 5 mA). La disipación de energía en este modo es solo ligeramente mayor que cuando el dispositivo está en modo apagado. Es posible reducir aún más el consumo de energía en modo de bajo consumo disminuyendo el voltaje de salida nominal del modo activo mediante uno de las desviaciones programadas internamente de 50, 100, 150 y 200 milivoltios.

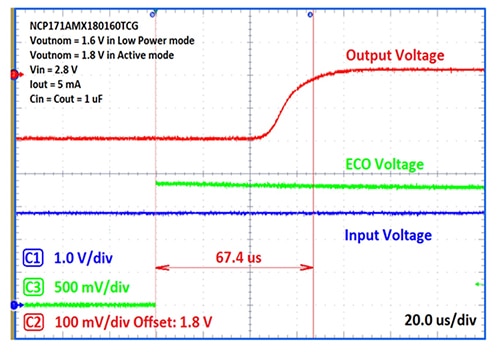

La ventaja clave del modo de bajo consumo es el tiempo de respuesta a una demanda de voltaje regulado normal. Cuando se lleva a alto (igual a VOUT), el pin ECO cambia el dispositivo al modo activo y restaura el LDO NCP171 al voltaje regulado y una IOUT máxima de hasta 80 mA en menos de 100 µs (Figura 4).

Figura 4: Cambiar el NCP171 del modo de bajo consumo al modo activo restaura el voltaje regulado en menos de 100 µs. (Fuente de la imagen: ON Semiconductor)

Figura 4: Cambiar el NCP171 del modo de bajo consumo al modo activo restaura el voltaje regulado en menos de 100 µs. (Fuente de la imagen: ON Semiconductor)

Cuando se inicia, el NCP171 pasa por defecto al modo activo, independientemente del estado del pin ECO, para que rápidamente pueda alcanzar el voltaje de salida objetivo y estabilizarse. La duración de este modo activo forzado es generalmente de 35 milisegundos (ms) y asegura una carga rápida del condensador de salida y un rápido aumento de la IOUT para satisfacer la demanda de la carga.

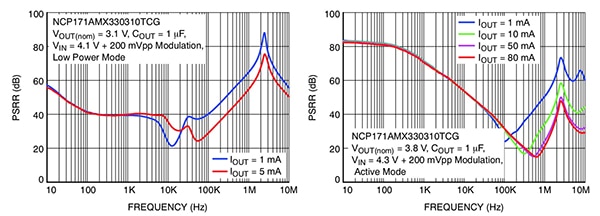

Hay algunas desventajas cuando se opera en modo de bajo consumo: La PSRR (relación de rechazo de la fuente de alimentación), una medida de la capacidad del LDO para rechazar picos de voltaje de entrada, es menor y el ruido eléctrico aumenta ligeramente (Figura 5).

Figura 5: Cuando el NCP171 está en modo de bajo consumo, la PSRR generalmente es más baja, en comparación con cuando está en modo activo. (Fuente de la imagen: ON Semiconductor)

Figura 5: Cuando el NCP171 está en modo de bajo consumo, la PSRR generalmente es más baja, en comparación con cuando está en modo activo. (Fuente de la imagen: ON Semiconductor)

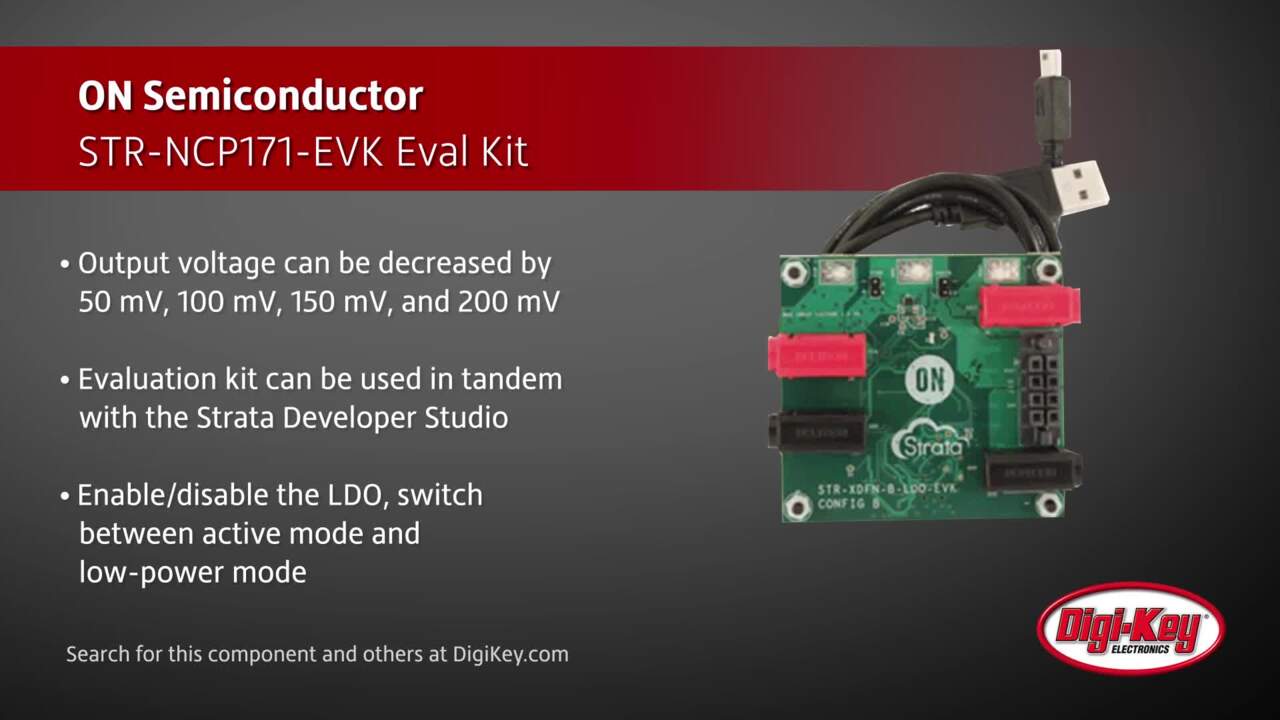

El LDO NCP171 viene acompañado del EVK (kit de evaluación) STR-NCP171-EVK. El EVK se diseñó para usarse con el IDE (entorno de desarrollo integrado) Strata Developer Studio de ON Semiconductor, que se ejecuta en una PC. El EVK se conecta al IDE a través de un cable USB y luego se puede utilizar para experimentar las capacidades del LDO, por ejemplo, habilitar y deshabilitar el LDO y cambiar entre los modos activo y de bajo consumo.

El EVK y el IDE también le permiten al ingeniero configurar y monitorear otros parámetros operativos del LDO, incluidos el voltaje de entrada y salida, la disipación de potencia y la temperatura del dispositivo.

Conclusión

Un LDO cuidadosamente seleccionado simplifica el diseño de la fuente de alimentación de un dispositivo portátil, al tiempo que garantiza un voltaje y una corriente estables. Al seleccionar un LDO con una baja corriente a tierra y minimizar la diferencia entre su voltaje de entrada y salida, el diseñador puede lograr una eficiencia cercana a la de un regulador de conmutación.

La vida útil de la batería portátil se puede mejorar aún más seleccionando un LDO de una nueva generación que ofrece modos operativos, los que se seleccionan de un pin determinado y cuyo diseño permite limitar la disipación de potencia mientras el dispositivo portátil está en modo de suspensión durante un período prolongado. Los proveedores de silicio suelen acompañar el LDO con herramientas de evaluación que permiten al diseñador experimentar las mejores configuraciones del dispositivo para maximizar la vida útil de la batería.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.