Principios analógicos: Cómo funcionan los circuitos de muestreo y retención y cómo asegurar la precisión del ADC

Colaboración de Editores de DigiKey de América del Norte

2020-04-22

La conversión de una señal analógica del mundo "real" a una señal digital que pueda ser procesada en sentido ascendente es una función fundamental de los sistemas electrónicos, que van desde la grabación de audio hasta la Internet de las Cosas (IO), la IO Industrial (IOT), y ahora la inteligencia artificial (IA) de las cosas (IOT). Sin embargo, para llevarla a cabo con eficacia y eficiencia es necesario un nivel de comprensión de los principios y medidas subyacentes que a menudo se pasan por alto.

Por ejemplo, ¿cómo se "retiene" y luego se "muestrea" exactamente una señal antes de la conversión, dado que una señal analógica común aplicada a la entrada de un convertidor analógico-digital (ADC) cambia continuamente de amplitud y será diferente al final de la conversión que al principio? Este cambio de amplitud o sesgo puede dar lugar a un grave error, especialmente para las SAE de alta resolución que tardan más tiempo en convertir una señal. El desafío para los diseñadores es entender y eliminar esta fuente de error.

Este artículo muestra cómo se logra evitar la desviación de la amplitud utilizando un circuito de muestra y retención (S&H) o de seguimiento y retención (T&H) para el ADC. El S&H (o T&H) realiza el verdadero muestreo de la entrada y opera entre el filtro de paso bajo antialiasing de la entrada y el ADC. El artículo analiza las características y los criterios de selección de los CI de S&H y examina los ADC con CI de S&H integrado. A título ilustrativo se utilizan dispositivos de ejemplo con características diversas para diferentes aplicaciones de Texas Instruments, Maxim Integrated y Analog Devices.

Función de la toma de muestras y retención en ADC

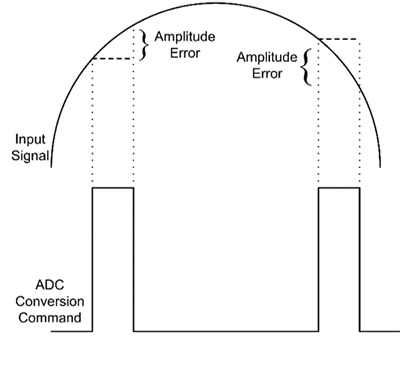

Cuando se aplica una señal no CC a la entrada de un ADC, esta cambia de amplitud continuamente. Sin embargo, el proceso de conversión analógico-digital toma un intervalo de tiempo finito, por lo que a lo largo de ese tiempo, la amplitud de la entrada del ADC cambiará (Figura 1). Es esta desviación de la amplitud lo que resulta en un error potencialmente grave.

Figura 1: Un SAE con una señal de entrada variable está sujeto a errores de amplitud (arriba) debido a las variaciones de amplitud de la señal durante la digitalización (abajo). (Fuente de la imagen: DigiKey)

Figura 1: Un SAE con una señal de entrada variable está sujeto a errores de amplitud (arriba) debido a las variaciones de amplitud de la señal durante la digitalización (abajo). (Fuente de la imagen: DigiKey)

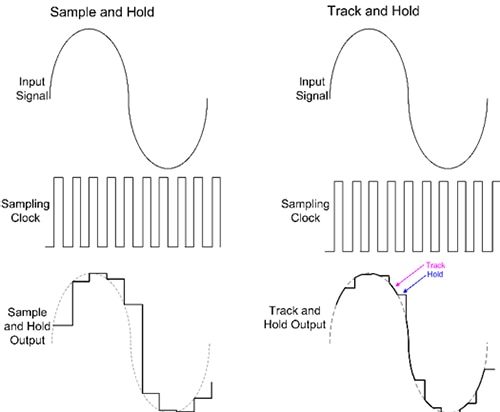

La prevención de la desviación de la amplitud en un SAE consiste en muestrear la señal y mantener una amplitud fija mientras se realiza la conversión. Esto se logra usando el circuito S&H o T&H para el ADC (Figura 2).

Figura 2: La principal diferencia entre un circuito S&H (izquierda) y un T&H (derecha) es la duración del período de seguimiento: es corto en el S&H y largo en el T&H. (Fuente de la imagen: DigiKey)

Figura 2: La principal diferencia entre un circuito S&H (izquierda) y un T&H (derecha) es la duración del período de seguimiento: es corto en el S&H y largo en el T&H. (Fuente de la imagen: DigiKey)

Ambos tipos de circuitos muestrean la señal de entrada y mantienen constante el voltaje muestreado durante todo el proceso de conversión. La salida del circuito T&H (derecha) sigue la señal de entrada hasta que se le indica que muestre; luego mantiene el valor de la muestra durante la conversión ADC. El S&H tiene una apertura de muestra más corta y su salida es una serie de niveles de muestra (izquierda). La diferencia clave entre T&H y S&H es la duración del intervalo de seguimiento: muy corto para el S&H y significativamente más largo para el T&H. Ambos circuitos dependen de un interruptor rápido para aislar un capacitor de almacenamiento que ha sido conectado a la entrada de la señal. El resto de este artículo utilizará S&H como sinónimo de S&H o T&H.

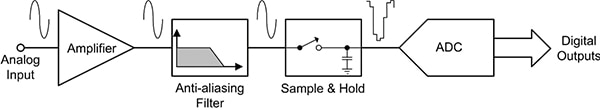

La etapa S&H realiza el verdadero muestreo de la entrada y opera entre el filtro de paso bajo antialiasing de la entrada y el ADC. El filtro de paso bajo realiza una limitación de banda antialiasing y debe preceder al S&H para limitar la señal antes de la toma de muestras para evitar el aliasing (Figura 3).

Figura 3: En la ruta de la señal del digitalizador, el S&H se coloca entre el filtro de paso bajo anti-aliasing y el ADC. (Fuente de la imagen: DigiKey)

Figura 3: En la ruta de la señal del digitalizador, el S&H se coloca entre el filtro de paso bajo anti-aliasing y el ADC. (Fuente de la imagen: DigiKey)

Observe que las señales anteriores al S&H son todas señales analógicas. La salida del S&H es una forma de onda muestreada que se alimenta al ADC.

Un típico dispositivo S&H

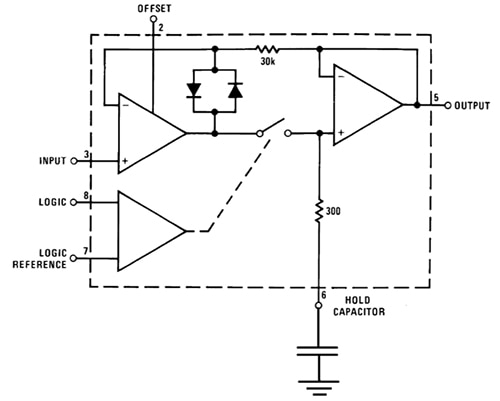

El diagrama de bloques del circuito integrado (CI) S&H LF398MX/NOPB de Texas Instruments muestra la configuración básica del circuito (Figura 4). El S&H se implementa usando un interruptor rápido y un capacitor de alta calidad. En el caso del LF398MX/NOPB, el capacitor es externo al CI. Cuando el interruptor se cierra, el capacitador se carga al nivel de voltaje de la señal de entrada. Cuando el interruptor está abierto, el capacitador retiene ese voltaje hasta que es digitalizado por el ADC. Este S&H utiliza la tecnología bi-FET, que combina FET con transistores bipolares, para soportar una adquisición rápida (menos de 6 microsegundos (µs) con un error de amplitud del 0.01%) con una alta precisión de CC (generalmente 0.002%), y una caída de voltaje extremadamente baja (generalmente menos de 83 microvoltios (µV) por segundo). Los amplificadores internos amortiguan el interruptor y mantienen el capacitador.

El tiempo de adquisición del S&H depende del valor del capacitador de retención, que puede estar en el rango de 0.001 a 0.1 microfaradios (µF). El capacitor de retención externa tiene que tener una baja absorción dieléctrica y bajas fugas. Se recomiendan capacitores de poliestireno, polipropileno y teflón.

Figura 4: El diagrama de bloques de LF398MX/NOPB S&H de Texas Instruments muestra los componentes claves: un interruptor rápido y un capacitor de retención externo. (Fuente de la imagen: Texas Instruments)

Figura 4: El diagrama de bloques de LF398MX/NOPB S&H de Texas Instruments muestra los componentes claves: un interruptor rápido y un capacitor de retención externo. (Fuente de la imagen: Texas Instruments)

Características de S&H

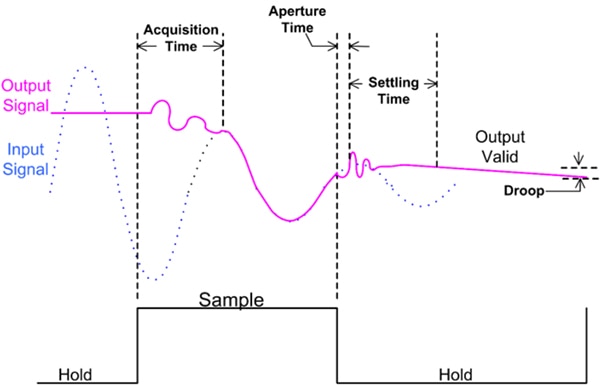

Los dispositivos de S&H tienen una serie de términos específicos para describir su funcionamiento (Figura 5).

Figura 5: Las definiciones de las características dinámicas comunes de S&H incluyen el tiempo de adquisición, el tiempo de asentamiento, el tiempo de apertura y la caída de la amplitud. (Fuente de la imagen: DigiKey)

Figura 5: Las definiciones de las características dinámicas comunes de S&H incluyen el tiempo de adquisición, el tiempo de asentamiento, el tiempo de apertura y la caída de la amplitud. (Fuente de la imagen: DigiKey)

El tiempo de adquisición es el tiempo que transcurre desde que se cambia a modo de muestra hasta que el S&H comienza a rastrear la señal de entrada. Es una función del valor del capacitor de retención y la resistencia en serie del interruptor y la trayectoria de la señal. Cuando el modo vuelve a estar en espera, puede haber un retraso hasta que el dispositivo deje de rastrear la entrada y comience a mantener un valor: éste es el tiempo de apertura. El tiempo de apertura es una función de los retardos de propagación de los conductores y del interruptor. La incertidumbre o fluctuación de la apertura es la variación del tiempo de apertura debido a las variaciones del reloj y al ruido.

Una vez en el modo de espera, hay un tiempo entre el momento en que se entra en ese modo y el momento en que el dispositivo se ajusta dentro de una banda de error sobre el valor de espera llamado tiempo de ajuste o de ajuste de espera. Parte del tiempo de asentamiento puede incluir una transferencia no deseada de carga entre el conductor del interruptor y el capacitor de retención; esto se llama el paso de retención o error de pedestal. El paso de retención suele tener magnitudes en el rango de milivoltios (mV) y su efecto se minimiza manteniendo el rango de escala completa de las señales lo más alto posible.

El período de muestreo más corto para el S&H es la suma del tiempo de adquisición, el tiempo de apertura y el tiempo de asentamiento. La máxima tasa de muestreo posible es la recíproca de la suma del tiempo de adquisición, el tiempo de apertura y el tiempo de asentamiento.

Mientras está en el modo de retención, el valor de retención de S&H puede disminuir debido a la fuga del capacitor de retención. Este incremento de voltaje se llama caída. Se suele especificar como una tasa de caída en mV por segundo.

Configuraciones S&H

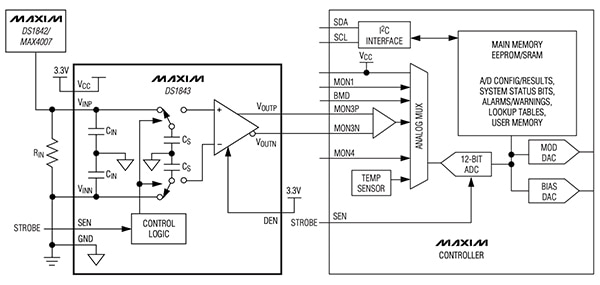

Los CI de S&H están disponibles en muchas configuraciones para adaptarse a las necesidades de la aplicación. Considere una aplicación que requiera entradas diferenciales como la interfaz con un transductor de salida diferencial como un acelerómetro, una banda extensométrica o un monitor óptico de corriente. El DS1843D+TRL de Maxim Integrated es un buen ejemplo de un CI de S&H para tales aplicaciones (Figura 6).

Figura 6: Tal como se muestra en este típico circuito de funcionamiento, el DS1843+TRL de Maxim Integrated es un S&H diferencial que utiliza capacitores de doble retención para implementar el muestreo diferencial. (Fuente de la imagen: Maxim Integrated).

Figura 6: Tal como se muestra en este típico circuito de funcionamiento, el DS1843+TRL de Maxim Integrated es un S&H diferencial que utiliza capacitores de doble retención para implementar el muestreo diferencial. (Fuente de la imagen: Maxim Integrated).

El DS1843+TRL que se muestra está en una típica aplicación de transmisión de línea óptica para la medición del indicador de intensidad de la señal recibida en modo ráfaga (RSSI). El DS1842/MAX4007 de Maxim Integrated es un monitor de corriente que refleja la corriente de un fotodiodo de avalancha conectado a su entrada de referencia. La corriente de salida se dirige a través de la resistencia, RIN, convirtiéndola en un voltaje. Esta tensión se mide de manera diferencial mediante el DS1843, que consta de interruptores y capacitores de muestreo totalmente diferenciales, CS y un búfer de salida diferencial. Este S&H utiliza dos capacitores de 5 picofaradios (pF), uno conectado a la entrada diferencial positiva y el otro a la entrada diferencial negativa. El bajo valor de capacitancia asegura un rápido tiempo de adquisición. Este dispositivo tiene un tiempo de muestreo (adquisición) rápido de menos de 300 nanosegundos (ns). El tiempo de retención del S&H es mayor de 100 µs.

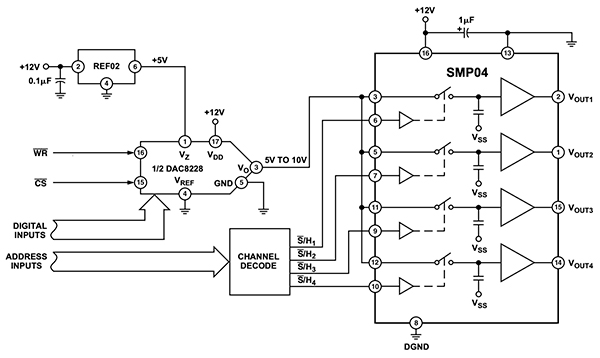

Hay dispositivos disponibles que contienen cuatro u ocho circuitos de S&H en un solo paquete de CI. Un ejemplo es el quad S&H de la serie SMP04ESZ-REEL de de Analog Devices. El SMP04ESZ-REEL es un dispositivo CMOS que incorpora cuatro circuitos de S&H en un paquete común y presenta un tiempo de adquisición de 7 µs y una tasa de caída de solo 2 mV/s (Figura 7).

La figura 7 también ilustra cómo S&H puede utilizarse con los convertidores digitales-analógicos (DAC), en este caso para evitar los transitorios de salida o los fallos causados por las transiciones de código en el DAC.

Figura 7: Los quad S&H de la serie SMP04 de Analog Devices contienen cuatro circuitos independientes S&H junto con amplificadores de búferes correspondientes. El circuito mostrado utiliza el SMP04 que se usa para multiplexar la salida de un DAC en cuatro canales. (Fuente de la imagen: Analog Devices).

Figura 7: Los quad S&H de la serie SMP04 de Analog Devices contienen cuatro circuitos independientes S&H junto con amplificadores de búferes correspondientes. El circuito mostrado utiliza el SMP04 que se usa para multiplexar la salida de un DAC en cuatro canales. (Fuente de la imagen: Analog Devices).

En la figura, el SMP04 se utiliza para multiplexar la salida de un DAC, dividiendo la salida de un DAC en cuatro canales multiplexados. Los circuitos S&H pueden utilizarse para retrasar selectivamente la salida del DAC hasta después del fallo, suavizando así la salida del DAC.

Se pueden utilizar múltiples circuitos S&H para aumentar el rendimiento de un ADC mediante la canalización de entradas multiplexadas. Aquí, múltiples S&H están conectados en común a la salida del multiplexor. El ADC está conectado a un S&H, que mantiene el nivel de entrada para una conversión. Los otros S&H adquieren otros canales multiplexados y, a su vez, se conectan al ADC, mientras que el primer S&H está libre para conectarse a otro canal multiplexado. Esta técnica de canalización elimina el tiempo de adquisición de S&H en la trayectoria de la señal del ADC.

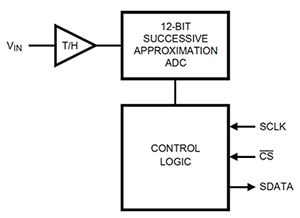

Muchos ADC incorporan circuitos S&H o T&H dentro de su paquete integrado. Un ejemplo es el ADC121S021CIMFX de Texas Instruments, un ADC del registro de aproximación sucesiva (SAR) de 12 bits con T&H incorporado que funciona con tasas de muestreo del orden de 50 a 200 kilomuestras por segundo (kS/s). Tiene un bus de salida serial de alta velocidad que simplifica la disposición del cableado (Figura 8).

Figura 8: El ADC121S021 de Texas Instruments es un ADC SAR de un solo canal de 12 bits con un circuito T&H incorporado. (Fuente de la imagen: Texas Instruments)

Figura 8: El ADC121S021 de Texas Instruments es un ADC SAR de un solo canal de 12 bits con un circuito T&H incorporado. (Fuente de la imagen: Texas Instruments)

Este ADC es una pieza común en muchos circuitos integrados de ADC, ya que cuenta con un T&H interno, que simplifica la disposición de la placa de la PC y ayuda a minimizar el número de componentes. Los circuitos T&H externos se utilizan para configuraciones especiales como conexiones de entrada diferencial, entradas multiplexadas o cuando el ADC no tiene un circuito T&H o S&H interno.

Conclusión

Desde la grabación de audio hasta el más avanzado análisis de IIoT o AI, la función electrónica más básica de convertir una señal analógica en una digital requiere una cuidadosa atención a los circuitos S&H o T&H. Son esenciales para minimizar los errores de sesgo de voltaje durante el proceso de conversión analógico-digital, ya que mantienen constante el voltaje de entrada al ACD durante la conversión. El S&H puede ser interno o externo, pero debe estar en la ruta de la señal entre el filtro antialiasing de paso bajo y el ADC. Como se muestra, hay muchas configuraciones -un solo, diferencial o múltiples dispositivos por CI para satisfacer una variedad de aplicaciones de diseño. Estas aplicaciones se extienden para incluir la prevención de los transitorios de salida o los fallos causados por las transiciones de código en los DAC.

Lecturas recomendadas

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.