Asociar el ADC correcto con la aplicación

Colaboración de Editores de DigiKey de América del Norte

2018-04-03

Es un mundo analógico controlado por computadoras digitales. Como tal, los diseñadores de dispositivos de Internet de las cosas (IoT) necesitan convertir eficientemente los valores analógicos en representaciones digitales muestreadas. Si bien la respuesta simple puede parecer simplemente colocar un convertidor analógico a digital (ADC) de frente, no todos los ADC son iguales. Por lo tanto, los diseñadores deben comprender las diversas topologías y cómo se asignan a la aplicación.

Por ejemplo, los ADC se han diseñado para optimizar características como la velocidad de muestreo, el consumo de energía y la precisión. Este artículo discutirá los requisitos de diseño en el contexto de algunas arquitecturas comunes de ADC. A continuación, se presentarán las aplicaciones que emplean estas arquitecturas y se mostrará cómo se implementan.

El papel de un ADC

El ADC es un circuito integrado electrónico o dispositivo modular de uso común que convierte una señal analógica, generalmente un voltaje, en una serie de representaciones digitales discretas muestreadas, o en números. Los ADC realizan tres operaciones distintas: muestreo, cuantificación y codificación. Forman el corazón de muchos instrumentos digitales comunes, como voltímetros, osciloscopios y analizadores de espectro. También se incorporan en el front end de los circuitos digitales que procesan señales analógicas provenientes de dispositivos como micrófonos, acelerómetros, y otros transductores que necesitan convertir su salida al dominio digital para que un microprocesador pueda trabajar con los datos.

Hay muchas arquitecturas de ADC, o topologías, que se han desarrollado para muestrear y digitalizar señales analógicas. Cada forma del ADC tiene sus propias características, beneficios y debilidades. La elección de un tipo específico de ADC para una aplicación dada generalmente se define por los requisitos de medición de velocidad, resolución, precisión, consumo de energía y tamaño físico.

Características principales de un ADC

La primera operación que un ADC debe realizar es muestrear la señal analógica. El muestreo se realiza mediante un circuito de muestreo y retención o de seguimiento y retención. El muestreo o el teorema de Nyquist requiere que la velocidad de muestreo sea mayor que el doble del ancho de banda de la señal para poder reconstruir la señal analógica de las muestras digitalizadas. Por lo tanto, la primera característica significativa del ADC es la velocidad de muestreo, que determina el componente de frecuencia de señal máxima que se puede digitalizar.

El ADC debe cuantificar cada muestra y dividir el voltaje muestreado en un número finito de niveles de amplitud discretos. Esta característica generalmente se describe como el número de bits de resolución. Por ejemplo, si una señal se divide en 8 bits, significa que hay 28 o 256 niveles discretos. Un ADC de 16 bits el rango de voltaje en 65,536 niveles de cuantificación.

Tanto la resolución como la velocidad máxima de muestreo están determinadas por el hardware del ADC. En general, cuanto mayor es la resolución del ADC, más limitada es la velocidad máxima de muestreo.

La precisión de un ADC depende tanto de la resolución como de la velocidad de muestreo. La resolución afecta la precisión y la exactitud de la amplitud. Otros factores que afectan la precisión de la amplitud son la linealidad del proceso de cuantificación y los efectos del ruido vertical. La frecuencia de muestreo determina la precisión y la exactitud de la temporización.

El tamaño físico y el consumo de energía son otros atributos que dependen de la topología del circuito. Son las principales preocupaciones para las aplicaciones que tienen un tamaño o potencia disponible limitados, como dispositivos IoT o instrumentos portátiles que funcionan con baterías. El tamaño físico y el consumo de energía dependen en gran medida de la topología del ADC.

¿Flash, directo o paralelo?

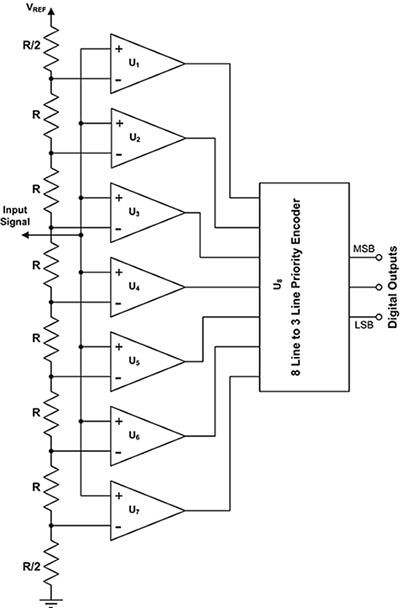

El digitalizador más simple conceptualmente es el ADC flash. Este también es conocido como ADC directo o paralelo (Figura 1).

Figura 1: El ADC flash utiliza comparadores múltiples con voltajes de umbral uniformemente incrementados para convertir un voltaje analógico en un número digital. Este ejemplo muestra un ADC de 3 bits con una resolución de 8 niveles. (Fuente de la imagen: DigiKey)

La entrada al ADC flash, por lo general, proviene de un circuito de muestreo y retención o de seguimiento y retención, donde la entrada analógica se muestrea y se mantiene constante durante la conversión. La señal muestreada se aplica a una matriz de comparadores analógicos con voltajes de umbral que están uniformemente espaciados sobre el rango de voltaje de entrada del ADC en un valor igual a un bit menos significativo (LSB). La salida de cada comparador cambia de estado si el voltaje de entrada excede el umbral establecido para ese comparador por el divisor de voltaje. El ejemplo en la figura muestra un ADC de 3 bits que requiere 7 comparadores para producir 8 estados posibles.

En general, un convertidor de flash de N bits requiere comparadores (2N-1). Los comparadores producen lo que se llama un "código de termómetro". Cuanto mayor sea el voltaje de entrada, mayor será el número de comparadores que alcancen su estado "1" de abajo hacia arriba. Este código se aplica a un codificador de prioridad que convierte este código en un código binario.

La principal ventaja del convertidor de flash es la velocidad. El tiempo de conversión solo incluye el retraso del comparador y el decodificador. Los convertidores flash con velocidades máximas de muestreo que alcanzan 5 gigamuestras por segundo (GS/s) están disponibles comercialmente. El factor limitante para la resolución del convertidor flash es la cantidad de comparadores requeridos. Un ADC flash de 8 bits requeriría 255 comparadores.

Este número aumenta en un factor de dos por cada bit de resolución aumentada. Esto significa que el tamaño físico del ADC crece exponencialmente con la resolución. Esto conduce a la otra limitación, que es la potencia requerida por el convertidor flash. Esto limita su uso a las aplicaciones con alimentación de línea. El límite práctico para la resolución flash es de aproximadamente 8 bits.

Codificación binaria

La salida binaria del ADC se puede codificar de varias maneras. Si la señal que se convierte es unipolar, entonces generalmente se codifica como un código binario unipolar. Este código representa un valor de cero como todos ceros (0000...) y el valor máximo de entrada como todos unos (1111...).

Si la señal es bipolar, entonces se representa generalmente como binario de compensación o binario de complemento a dos como se detalla usando un ejemplo de 4 bits (Tabla 1).

|

Tabla 1: Codificación binaria común para señales digitales bipolares. El binario de complemento a dos es el más ampliamente utilizado por los procesadores matemáticos o microprocesadores. (Fuente de la imagen: DigiKey)

La codificación binaria de complemento a dos es el tipo de codificación utilizado por la mayoría de los sistemas basadose en microprocesadores o procesadores matemáticos, ya que facilita operaciones aritméticas.

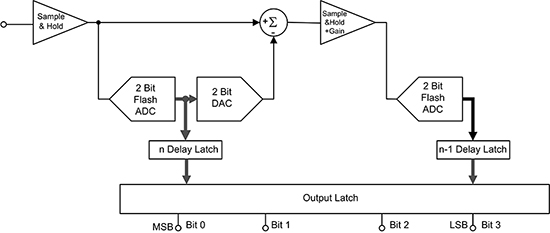

Convertidores ADC de dos pasos, de subrango y de canalización

El número de comparadores en un convertidor flash se puede reducir al dividir la conversión en dos o más pasos y convertir un número menor de bits por etapa. Si el ADC flash está dividido en dos secciones, se denomina ADC de dos pasos o de subrango. Si se divide en más de dos secciones, se denomina ADC de canalización. Un ADC de dos pasos aún puede muestrear a cientos de megamuestras por segundo (MS/s) (Figura 2).

Figura 2: Un diagrama de bloques funcionales de un ADC de 4 bits, de dos pasos o de subrango muestra que divide el convertidor de 4 bits en dos convertidores de 2 bits para disminuir el número de comparadores. (Fuente de la imagen: DigiKey).

Este convertidor de dos pasos divide el convertidor de 4 bits, que requeriría 15 comparadores, en dos secciones de 2 bits. Cada sección usa tres comparadores para un total de seis comparadores. El convertidor opera al convertir los dos bits más significativos (MSB) primero. La salida digital de la primera sección incluye un convertidor digital a analógico (DAC) para convertir la señal a analógica y restarla de la señal de entrada.

La diferencia resultante se amplifica y se usa para convertir los dos LSB. Los resultados combinados se capturan en los de salida. El proceso de conversión se repite dos veces, por lo que la velocidad máxima de muestreo será menor que la del convertidor flash. El AD9203ARUZRL7 de Analog Deviceses un ejemplo de un ADC de canalización de 10 bits, de 40 MS/s que resuelve el problema de la conversión de analógico a digital a alta velocidad.

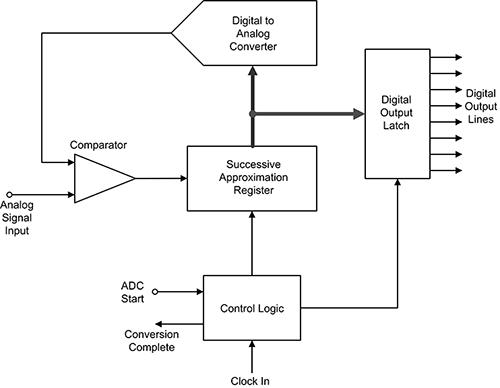

Convertidores ADC de registro de aproximaciones sucesivas (SAR)

Cuando la aplicación requiere una mayor resolución, y no necesariamente la velocidad del ADC flash o de canalización, el convertidor de registro de aproximaciones sucesivas (SAR) es una buena opción (Figura 3). Los ADC de SAR funcionan a 12 a 16 bits, con velocidades de muestreo de hasta 1 a 2 MS/s.

Figura 3: El ADC de SAR proporciona una buena resolución con requisitos de potencia baja a moderada. (Fuente de la imagen: DigiKey)

Al igual que el ADC flash, el ADC de SAR está precedido por un circuito de muestreo y retención o de seguimiento y retención para mantener el valor de muestra durante el proceso de conversión. La señal de muestreo y retención se aplica a un comparador. El registro de aproximación sucesiva comienza en el rango medio y convierte el valor a un voltaje analógico con el DAC.

Este voltaje de "conjetura" se compara con la entrada de señal en el comparador. Si la salida del comparador se mantiene baja, el valor de registro se incrementa en un cuarto del rango. Esencialmente, el valor de registro se reduce o aumenta en factores de dos pasos hasta que el comparador indique que el contenido del registro convertido por DAC es igual al voltaje de la señal de entrada. Cuando eso ocurre, el convertidor emite la señal de "conversión completa" y acopla el valor digital en el de salida.

El tiempo de conversión es proporcional a la resolución del ADC, que se establece por la longitud del registro. Los ADC de SAR proporcionan una buena resolución con requisitos de potencia baja a moderada. Un ejemplo de un SAR de bajo costo y baja energía es el MAX11665AUT-T de Maxim Integrated. Es un ADC de SAR de 12 bits y 500 kilomuestras por segundo (kS/s), por lo que se adapta bien a la digitalización de las salidas de los sensores.

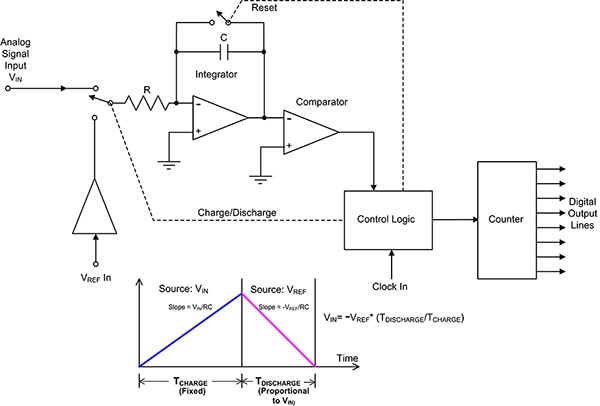

Integración del ADC de doble pendiente

La integración de los ADC ofrece alta resolución mientras minimiza los efectos del ruido. El ADC de doble pendiente es el ADC integrador más común (Figura 4).

Figura 4: El diagrama de bloques de un ADC integrador de doble pendiente que incluye un gráfico que muestra cómo se usa la de carga/descarga para determinar el voltaje de entrada desconocido. (Fuente de la imagen: DigiKey)

Inicialmente, la entrada está conectada al integrador. El capacitor, C, se carga por la señal de entrada durante un tiempo fijo. Al finalizar el tiempo de carga, el integrador se conecta al voltaje de referencia. Esto descarga el capacitor a cero como lo determina el comparador. Un contador mide el tiempo que toma descargar el capacitor. El tiempo es proporcional al voltaje de entrada impreso en el capacitor durante el ciclo de carga. Una relación simple basada en el tiempo de carga conocido y el tiempo de descarga medido permite calcular el voltaje de entrada.

Debido a que la entrada de señal se aplica a un integrador, el efecto de promediado del integrador minimiza el efecto de cualquier señal de ruido. El convertidor de doble pendiente es ideal para aplicaciones de alta resolución que requieren alta precisión. Las resoluciones de 12 a 16 bits son comunes, con velocidades máximas de muestreo de hasta 100 KS/s.

La aplicación más conocida de los ADC de doble pendiente es para los voltímetros digitales (DVM o DMM). El modelo ICL7109CPL+ de ADC de 12 bits de Maxim Integrated con salidas de tres estados es un convertidor de doble pendiente diseñado para medir señales analógicas como presión, velocidad o flujo, a velocidades de hasta 30 veces por segundo.

El ADC sigma delta: alta resolución a bajas frecuencias

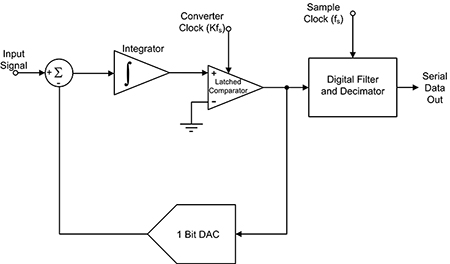

El ADC sigma delta ofrece la resolución más alta (de 16 a 24 bits) para señales de baja frecuencia. Al igual que el ADC de doble pendiente, es otro tipo de digitalizador integrador (Figura 5). La señal de entrada se aplica a través de un sumador al integrador. La salida del integrador se aplica a un comparador con traba donde se compara con una señal de cero voltios (de tierra). Si la salida integrada no es cero, la salida del comparador se retroalimenta para acercar la salida del integrador a cero. Este proceso se repite a la velocidad del reloj del convertidor hasta que la salida del integrador llegue a cero. La salida del comparador forma un flujo de datos en serie que es la salida digital del convertidor.

El ADC sigma delta se muestrea a una velocidad mucho más alta que la requerida para la velocidad de muestreo diseñada.

Obsérvese en la figura que el reloj del convertidor es más rápido que el reloj de muestreo de salida por un factor K. Las muestras adicionales de este "sobremuestreo" se utilizan para proporcionar un filtrado digital de la salida del convertidor. Un diezmador restaura la velocidad de muestreo de salida a la velocidad de reloj de muestra especificada.

El modelo AD7734BRUZ de ADC de Analog Devices es un digitalizador sigma delta de 24 bits y 4 canales diseñado para aplicaciones de control industrial y de proceso.

Figura 5: Un ADC sigma delta es ampliamente utilizado para la digitalización de alta resolución de señales de baja frecuencia para aplicaciones de audio, procesos y control industrial. (Fuente de la imagen: DigiKey)

En la Tabla 2 se proporciona un resumen de la resolución y la velocidad máxima de muestreo para los cinco tipos de ADC analizados.

|

Tabla 2: Características operativas del ADC para los cinco tipos de ADC discutidos en este artículo. (Fuente de la imagen: DigiKey)

Ejemplo de selección de topología

Considere una aplicación para digitalizar las señales de un telémetro ultrasónico portátil que utiliza un transductor de 40 kHz. Las reflexiones del objetivo son de -40 dB (1/100) de la amplitud del pulso transmitido.

La señal se debe muestrear a un mínimo del doble de la frecuencia de señal de 40 kHz. Es mejor muestrearla a cuatro o más veces 40 kHz, de modo que el rango de muestra deseado sea 160 kHz o más. Es una buena idea establecer una resolución que sea al menos diez veces los 40 dBm esperados, por lo que sería de 60 dB. La regla general es que cada 6 dB requiere 1 bit de resolución, por lo que se requerirá un ADC de 10 bits o más. Además, este es un instrumento portátil que considera el consumo de energía. Al consultar la Tabla 2, el convertidor de aproximación sucesiva sería la mejor opción. El MAX11665AUT-T de Maxim Integrated, mencionado anteriormente como ejemplo de un ADC de SAR, sería una buena opción para esta aplicación.

Conclusión

Como ambas no pueden lograrse simultáneamente, la elección de un ADC es principalmente una compensación entre la velocidad máxima de muestreo y la resolución. Otras consideraciones, tales como el tamaño físico y el consumo de energía, desempeñan un papel dependiendo de la aplicación y se les debe dar la debida ponderación en el proceso de selección.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.