Utilice módulos con amplificadores integrados para eliminar la "magia negra" del diseño de ADC de alta velocidad

Colaboración de Editores de DigiKey de América del Norte

2021-04-29

Los diseñadores de sistemas como los de adquisición de datos, hardware in the loop (HiL) y analizadores de potencia necesitan una cadena de convertidores de señales analógicas que pueda alcanzar una alta resolución y una gran precisión a velocidades de muestreo muy elevadas, a menudo de hasta 15 megamuestras por segundo (MSPS). Sin embargo, los diseños analógicos de alta velocidad pueden parecer "magia negra" para muchos diseñadores, especialmente cuando se enfrentan a una serie de parásitos ocultos que afectan a la integridad de la señal.

Por ejemplo, los diseños típicos son discretos y contienen varios circuitos integrados y componentes, como un amplificador totalmente diferencial (FDA), un filtro de paso bajo (LPF) de primer orden, una referencia de tensión y un convertidor analógico-digital (ADC) de alta velocidad y alta resolución. Las parásitas capacitivas y resistivas se encuentran dentro y alrededor del amplificador conductor del ADC (la FDA), el filtro de entrada del ADC y el ADC.

Eliminar, reducir o mitigar los efectos de estos parásitos es un reto. Requiere un alto grado de destreza y puede requerir muchos ciclos de diseño de circuitos e iteraciones de diseño de placas de circuito impreso, lo que compromete los calendarios de diseño y los presupuestos. Lo que se necesita es una solución más completa e integrada que resuelva muchos de estos problemas de diseño.

En este artículo se describe un circuito de adquisición de datos discreto y los problemas de diseño relacionados, y a continuación se presenta un módulo integrado que contiene un ADC de registro de aproximación sucesiva (SAR) de alta resolución y alta velocidad con una FDA front-end. El artículo muestra cómo el módulo completo ADAQ23875 de Analog Devices y su placa de desarrollo asociada superan los dolores de cabeza del diseño de alta velocidad, simplificando y acelerando el proceso de diseño sin dejar de obtener los resultados de conversión de alta resolución y alta velocidad requeridos.

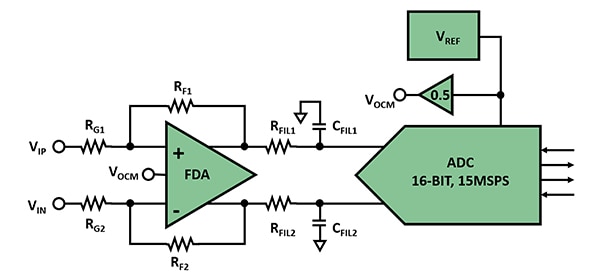

Ruta de la señal de adquisición de datos de alta velocidad

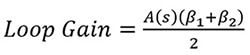

Los ADC de alto rendimiento utilizan entradas diferenciales para mejorar el rendimiento general equilibrando las señales de entrada y rechazando el ruido de modo común y las interferencias. Un controlador ADC analógico alcanza un rendimiento óptimo cuando las entradas al controlador ADC analógico y al ADC son totalmente diferenciales (Figura 1). El uso de una interfaz serie de señalización diferencial de bajo voltaje (LVDS) (derecha) permite que el sistema funcione a velocidades extremadamente altas para dar servicio a aplicaciones de adquisición de datos, HiL y analizadores de potencia.

Figura 1: Un sistema de adquisición de datos de alta frecuencia con una FDA front-end, un filtro analógico de primer orden y un SAR-ADC de entrada diferencial con una interfaz serial LVDS de alta velocidad. (Fuente de la imagen: Bonnie Baker)

Figura 1: Un sistema de adquisición de datos de alta frecuencia con una FDA front-end, un filtro analógico de primer orden y un SAR-ADC de entrada diferencial con una interfaz serial LVDS de alta velocidad. (Fuente de la imagen: Bonnie Baker)

La configuración de la figura 1 realiza muchas funciones esenciales, como el escalado de amplitud, la conversión de monofásico a diferencial, la amortiguación, el ajuste del desplazamiento en modo común y el filtrado.

Tecnología de controladores de la FDA

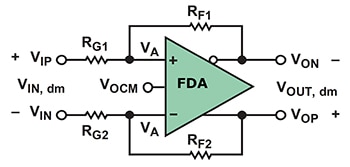

El funcionamiento del controlador ADC de retroalimentación de tensión de la FDA es como el de un amplificador tradicional, salvo por dos diferencias. En primer lugar, la FDA tiene una salida diferencial con un terminal de salida negativo adicional (VON). En segundo lugar, tiene un terminal de entrada añadido (VOCM) que establece la tensión de modo común de salida (Figura 2).

Figura 2: La FDA tiene dos entradas con bucles de retroalimentación y control de tensión (VOCM) de la tensión de modo común de salida. Esta configuración crea una entrada diferencial (VIN, dm) y una salida diferencial (VOUT, dm) independientes. (Fuente de la imagen: Analog Devices).

Figura 2: La FDA tiene dos entradas con bucles de retroalimentación y control de tensión (VOCM) de la tensión de modo común de salida. Esta configuración crea una entrada diferencial (VIN, dm) y una salida diferencial (VOUT, dm) independientes. (Fuente de la imagen: Analog Devices).

Internamente, la FDA tiene tres amplificadores: dos a la entrada y el tercero que actúa como etapa de salida. La retroalimentación negativa (RF1,RF2) y la alta ganancia en bucle abierto de dos amplificadores de entrada internos hacen que el comportamiento de los terminales de entrada, VA+ y VA-, sea prácticamente igual. En lugar de una salida de un solo extremo, la FDA produce una salida diferencial equilibrada entre VOP y VON, con una tensión en modo común de VOCM.

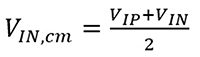

Las señales de entrada diferencial (VIP y VIN) son iguales en amplitud y opuestas en fase alrededor de una tensión de referencia en modo común (VIN, cm) con una señal de entrada equilibrada. Las ecuaciones 1 y 2 muestran cómo calcular la tensión de entrada en modo diferencial (VIN, dm) y la tensión de entrada en modo común (VIN, cm).

![]() Ecuación 1

Ecuación 1

Ecuación 2

Ecuación 2

Las ecuaciones 3 y 4 proporcionan las definiciones de salida diferencial y de modo común.

![]() Ecuación 3

Ecuación 3

![]() Ecuación 4

Ecuación 4

Obsérvese la adición del VOCM en la ecuación 4.

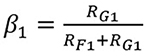

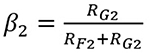

Como en los circuitos típicos de amplificación, la ganancia del sistema FDA depende de los valores de RGx y RFx. Las ecuaciones 5 y 6 definen los dos factores de retroalimentación de entrada, β1 y β2, para la FDA.

Ecuación 5

Ecuación 5

Ecuación 6

Ecuación 6

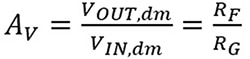

Cuando β1 es igual a β2, la ecuación 7 da la ganancia ideal en bucle cerrado para la FDA.

Ecuación 7

Ecuación 7

VOUT, dm permite conocer el rendimiento de los desajustes resistivos. La ecuación general de bucle cerrado para VOUT, dm incluye VIP, VIN, β1, β2 y VOCM. La ecuación 8 muestra la fórmula de VOUT, dm con la ganancia de tensión en bucle abierto del amplificador mostrada como A(s).

![VOUT,dm = [2 / β1 + β2] [VOCM(β1-β2)+VIP(1-β1)-VIN(1-β2) / 1 + 2/ A(S)(β1+β2)] Ecuación 8](http://sc-a.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2021/April/Use%20Modules%20with%20Integrated%20Amplifiers%20High-Speed%20ADC%20Design/article-2021april-use-modules-with-integrated-equation8.jpg?la=en&ts=fc1271d3-3f9d-4f4e-8cbc-609177a3d0b0) Ecuación 8

Ecuación 8

Cuando β1 ≠ β2, el error de la tensión de salida diferencial (VOUT, dm) depende principalmente de VOCM. Este resultado indeseable produce un desplazamiento y un exceso de ruido en la salida diferencial. Si β1 = β2 ≡ β, la ecuación 8 se convierte en la ecuación 9.

![VOUT,dm / VIN,dm = [RF/RG] [1 / 1 + 1/A(S)(β)] Ecuación 9](http://sc-c.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2021/April/Use%20Modules%20with%20Integrated%20Amplifiers%20High-Speed%20ADC%20Design/article-2021april-use-modules-with-integrated-equation9.jpg?la=en&ts=f057ce79-c262-4b25-a568-5a964b24c988) Ecuación 9

Ecuación 9

Los dos componentes del balance de salida son la amplitud y la fase. El equilibrio de la amplitud mide si las dos amplitudes de salida coinciden; lo ideal es que coincidan exactamente. El equilibrio de fase mide la proximidad de las diferencias de fase entre las dos salidas, con el ideal de 180°.

Las consideraciones de estabilidad de la FDA son las mismas que para los op-amps estándar. La especificación clave es el margen de fase. Las hojas de datos de los productos proporcionan el margen de fase de una configuración de amplificador concreta; sin embargo, los efectos parasitarios de la disposición de la placa de circuito impreso pueden reducir significativamente la estabilidad. En el caso de un amplificador de retroalimentación de tensión negativa, es bastante sencillo: la estabilidad depende de su ganancia de bucle, A(s) × β, el signo y la magnitud. La FDA, en cambio, tiene dos factores de retroalimentación. Las ecuaciones 8 y 9 tienen la ganancia del bucle en sus denominadores. La ecuación 10 describe la ganancia del bucle para el caso del factor de retroalimentación no emparejado (β1 ≠ β2).

Ecuación 10

Ecuación 10

La mitigación de todos los errores anteriores depende del tedioso y costoso proceso de adaptación con las resistencias discretas RG1, RG2,RF1 yRF2.

Rendimiento combinado de la FDA y el CAD

La FDA, las resistencias discretas, el filtro de primer orden y la combinación de ADC cuentan la historia de la relación señal-ruido (SNR), la distorsión armónica total (THD), la relación señal-ruido y distorsión (SINAD) y el rango dinámico libre de espurios (SFDR) que se suman a las características de rendimiento de la FDA en la precisión y resolución general del circuito. Las especificaciones combinadas incluyen la SNR, la THD, la SINAD y la SFDR. La FDA tiene numerosas especificaciones que afectan a estas especificaciones de frecuencia, como el ancho de banda, el ruido de la tensión de salida, la distorsión, la estabilidad y el tiempo de asentamiento, todo lo cual afecta al rendimiento del ADC. El ADC tiene su propio conjunto de especificaciones. El reto más importante es seleccionar la FDA adecuada para el CAD.

Diseño del tablero

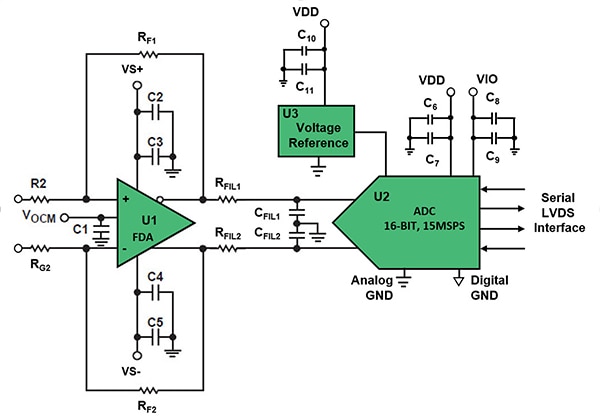

El diseño de la placa de circuito impreso es el último paso del proceso de diseño. Desgraciadamente, la disposición puede ser un paso de diseño que se pasa por alto, lo que da lugar a un diseño deficiente de la placa que puede comprometer o inutilizar el circuito. Este circuito discreto completo tiene tres circuitos integrados, seis resistencias y múltiples condensadores de desacoplamiento (Figura 3).

Figura 3: FDA y SAR-ADC con LPF de primer orden con condensadores de desacoplamiento de la fuente de alimentación. (Fuente de la imagen: Analog Devices).

Figura 3: FDA y SAR-ADC con LPF de primer orden con condensadores de desacoplamiento de la fuente de alimentación. (Fuente de la imagen: Analog Devices).

En la figura 3, los elementos parásitos que merman el rendimiento del circuito de alta velocidad son la capacitancia y la inductancia parásitas de la placa de circuito impreso. Las almohadillas de los componentes, las trazas, las vías y la tierra en paralelo con los planos de potencia son los culpables. Estas capacitancias e inductancias son especialmente peligrosas en los nodos de suma del amplificador, donde introducen polos y ceros en la respuesta de retroalimentación, causando picos e inestabilidad.

Solución integrada

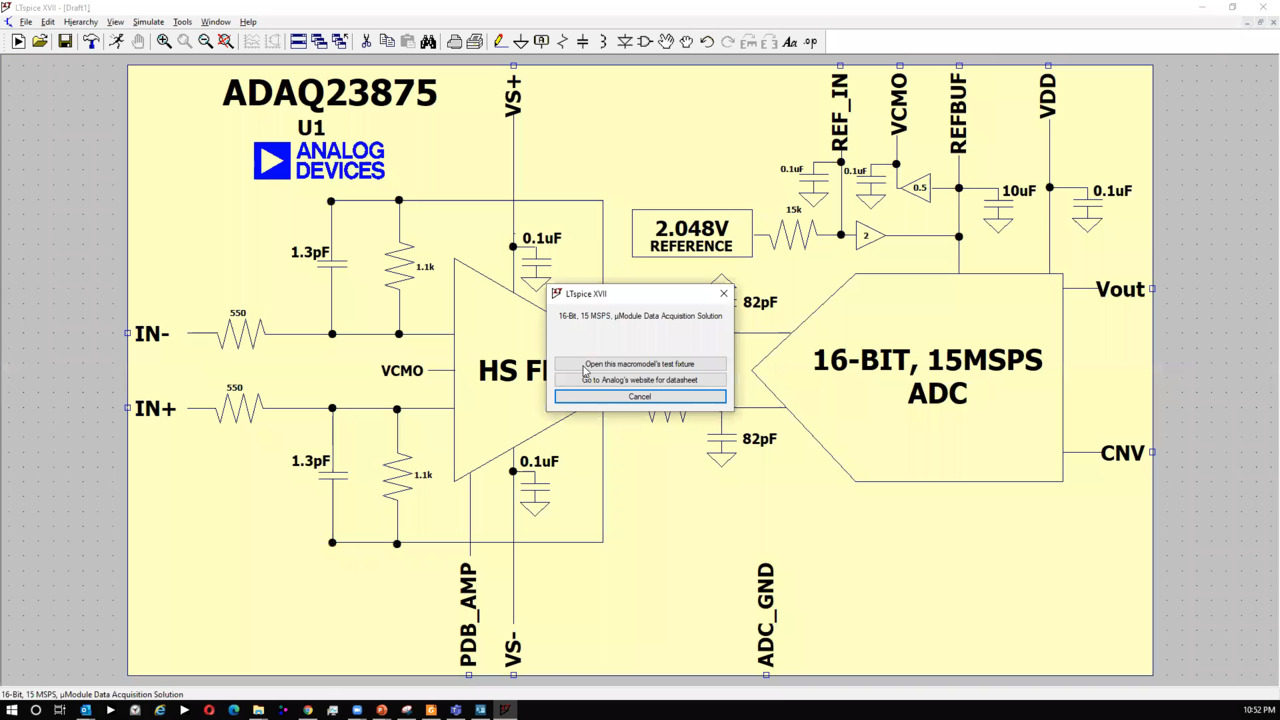

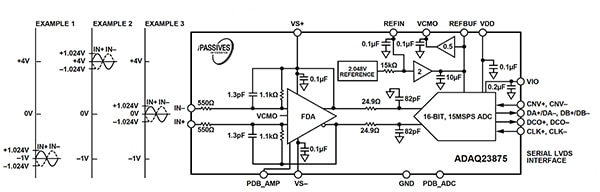

Los convertidores SAR pueden ofrecer una FDA, componentes pasivos cruciales, filtros de primer orden, una referencia de tensión y condensadores de desacoplamiento para mejorar la resolución efectiva. Por ejemplo, el ADAQ23875 de Analog Devices es un módulo de adquisición de datos de 16 bits y 15 MSPS con todos estos elementos (Figura 4). De este modo, reduce el ciclo de desarrollo de los sistemas de medición de precisión al transferir la carga de diseño de la selección de componentes, la optimización y la disposición del diseñador al circuito integrado.

Figura 4: El ADAQ23875 simplifica el diseño de los ADC de alta velocidad mediante la combinación de un FDA, un filtro de primer orden y un SAR-ADC en un único módulo apoyado por resistencias de ganancia ajustadas con láser alrededor del FDA, así como condensadores de desacoplamiento en el chip. (Fuente de la imagen: Analog Devices)

Figura 4: El ADAQ23875 simplifica el diseño de los ADC de alta velocidad mediante la combinación de un FDA, un filtro de primer orden y un SAR-ADC en un único módulo apoyado por resistencias de ganancia ajustadas con láser alrededor del FDA, así como condensadores de desacoplamiento en el chip. (Fuente de la imagen: Analog Devices)

Los componentes resistivos pasivos en el chip poseen características superiores de adaptación y deriva para minimizar las fuentes de error dependientes de los parásitos y ofrecen un rendimiento optimizado para garantizar la estrecha adaptación de β1 y β2. La coincidencia de estas ganancias de bucle ayuda a crear las especificaciones de ±1 milivoltio (mV) de desplazamiento del módulo y 91.6 microvoltios de ruido medio cuadrático total (µVRMS).

La referencia de tensión de 2,048 voltios de banda prohibida tiene un bajo nivel de ruido y una baja deriva (20 partes por millón por grado Celsius (ppm/°C)) para soportar el sistema FDA y ADC de 16 bits. Junto con la FDA, estas especificaciones se traducen en una precisión SAR-ADC de 90 dB SNR y una deriva de ganancia de ±1 ppm/°C. La patilla VOCM de la FDA utiliza los 2.048 voltios de la referencia para proporcionar su tensión de modo común de salida.

Un búfer de referencia interno multiplica por dos la referencia de 2.048 voltios para crear 4.096 voltios para la tensión de referencia del ADC. La diferencia de tensión entre la referencia del ADC y GND determina el rango de entrada a escala completa del SAR-ADC del ADAQ23875. Además, el ADAQ23875 tiene un condensador de desacoplamiento de 10 microfaradios (μF) en el chip entre el búfer de referencia y GND para absorber los picos de carga de conversión de referencia SAR-ADC y aliviar las limitaciones de diseño discreto.

Como muestra la figura 4, la tensión de modo común de entrada de la FDA es independiente de la tensión de modo común de salida de la FDA. En los ejemplos uno a tres, las fuentes de alimentación son:

VS+ = 7 voltios (fuente de alimentación positiva de la FDA)

VS- = -2 voltios (fuente de alimentación negativa de la FDA)

VDD = +5 voltios (fuente de alimentación del ADC)

VIO = 2,5 voltios (fuente de alimentación de salida analógica y digital)

El ejemplo 1 muestra un rango de voltaje de entrada de ±1.024 voltios con un voltaje de modo común de entrada de -1 voltios. La FDA aplica una ganancia de 2 voltios/voltios a estas señales, y el nivel de la FDA desplaza la tensión de salida por el valor en VCMO o 2.048 voltios. El proceso presenta un rango de señal de ±2.048 voltios con una tensión en modo común de VCMO de 2.48 voltios a la salida de la FDA. La frecuencia de esquina del filtro de primer orden es 1/(2pR x C) hertzios (Hz) o ~78 megahertzios (MHz). El rango de entrada de la señal al ADC es de ±2.048 voltios, con una tensión en modo común de +2.048 voltios.

El ADAQ23875 dispone de una interfaz digital LVDS con modos de salida de una o dos vías, lo que permite al usuario optimizar la velocidad de datos de la interfaz de cada aplicación. La alimentación digital de la interfaz es VIO.

El ADAQ23875 dispone de cuatro fuentes de alimentación: una alimentación interna del núcleo del ADC (VDD), una alimentación de la interfaz de entrada/salida digital (VIO), una alimentación positiva de la FDA (VS+) y una alimentación negativa (VS-). Para aliviar los problemas de diseño de la placa de circuito impreso, todos los pines de alimentación tienen condensadores de desacoplamiento en chip de 0.1 mF o 0.2 mF. Es necesario colocar condensadores cerámicos de desacoplamiento de 2.2 μF (0402, X5R) de buena calidad en la placa de circuito impreso a la salida de los reguladores LDO. Estos reguladores generan los raíles de alimentación del μModule (VDD, VIO, VS+ y VS-) para minimizar la susceptibilidad a las interferencias electromagnéticas (EMI) y reducir el efecto sobre los glitches de la línea de alimentación. Todos los demás condensadores de desacoplamiento necesarios están dentro del ADAQ23875, lo que mejora la relación de rechazo de la fuente de alimentación (PSRR) del subsistema en general, y ahorra espacio y costes adicionales en la placa. Para utilizar la referencia interna y el búfer de referencia interno, desacopla la patilla REFIN a GND con un condensador cerámico de 0.1 μF.

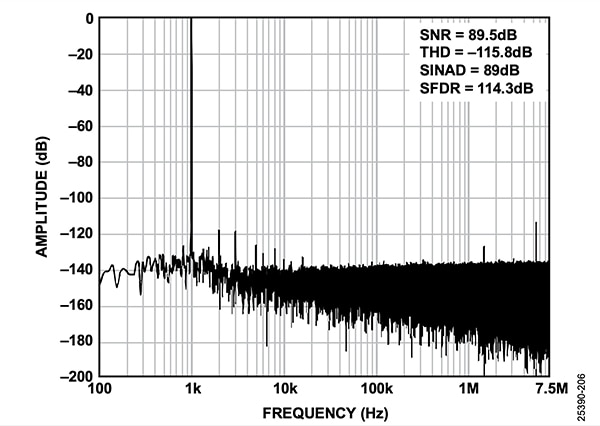

El módulo ADAQ23875 elimina los dolores de cabeza a la hora de seleccionar la FDA y la red resistiva adecuadas para el ADC, al tiempo que garantiza un alto rendimiento y unas especificaciones ajustadas de SNR, THD, SINAD y SFDR (89.5 dB, -115.8 dB, 89 dB y 114.3 dB, respectivamente) (Figura 5). Por lo general, la recopilación de las especificaciones del sistema corresponde al diseñador. El enfoque de sistema del ADAQ23875 ayuda a los diseñadores a conseguir estas especificaciones de forma más eficiente.

Figura 5: El módulo ADAQ23875 crea especificaciones de SNR, THD, SINAD, SFDR que pasan por la FDA en el chip, el filtro de primer orden y el SAR-ADC. (Fuente de la imagen: Analog Devices)

Figura 5: El módulo ADAQ23875 crea especificaciones de SNR, THD, SINAD, SFDR que pasan por la FDA en el chip, el filtro de primer orden y el SAR-ADC. (Fuente de la imagen: Analog Devices)

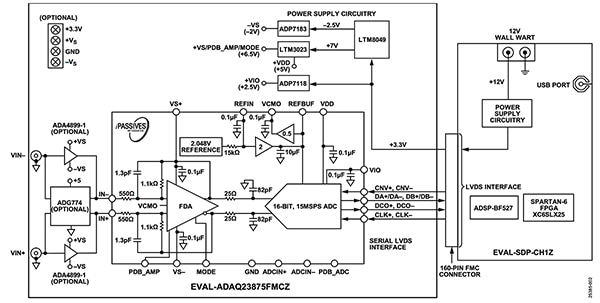

La Figura 5 muestra los resultados de las pruebas de SNR, THD, SINAD y SFDR para una señal de entrada diferencial de 1 kHz en el ADAQ23875. Para una aplicación específica, la tarjeta EVAL-ADAQ23875FMCZ para el ADAQ23875 dispone de un software que ayuda a las evaluaciones del dispositivo, incluyendo la programación del mismo, la forma de onda, el histograma y la captura de FFT. Los diseñadores pueden conectar la placa de evaluación a la plataforma de demostración del sistema EVAL-SDP-CH1Z de ADI para alimentarla y permitir el control de la placa de evaluación por un PC a través del puerto USB del SDP-CH1Z (Figura 6).

Figura 6: La placa de evaluación ADAQ23875FMCZ (izquierda) conectada a la placa de la plataforma de demostración del sistema (EVAL-SDP-CH1Z) (derecha), que permite controlar la placa de evaluación a través del puerto USB de un PC. (Fuente de la imagen: Analog Devices)

Figura 6: La placa de evaluación ADAQ23875FMCZ (izquierda) conectada a la placa de la plataforma de demostración del sistema (EVAL-SDP-CH1Z) (derecha), que permite controlar la placa de evaluación a través del puerto USB de un PC. (Fuente de la imagen: Analog Devices)

El software de la placa de evaluación, el complemento ACE para placa ADAQ23875 1.2021.8300 [Feb 18 21] y el software de instalación ACE 1.21.2994.1347 [Feb 08 21], permite al usuario configurar el valor de sobremuestreo de cada canal, el rango de entrada, el número de muestras y la selección del canal activo. Además, este software también permite guardar y abrir archivos de datos de prueba.

Conclusión:

Para superar los retos del diseño analógico de alta velocidad y ofrecer el mejor rendimiento global de adquisición de datos, los diseñadores pueden recurrir al módulo ADAQ23875. Se trata de un sistema completo de conversión de alta velocidad que incluye un FDA, un filtro de paso bajo de primer orden, un SAR-ADC y un conjunto de condensadores de desacoplamiento que amplifican las señales de excitación y proporcionan las señales de accionamiento adecuadas, así como el filtrado y la retroalimentación de las señales secundarias. El módulo del sistema de adquisición de datos ADAQ23875, un módulo altamente integrado, libra al diseño de la "magia negra" analógica con una solución completa FDA a SAR-ADC para la adquisición de datos de alta velocidad, hardware en el bucle (HiL) y analizadores de potencia.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.