Utilice microcontroladores sin Flash para reducir los costos del sistema y aumentar el rendimiento

Colaboración de Editores de DigiKey de América del Norte

2019-08-22

Debido a que a las redes de la Internet de las cosas (IoT) se les exige desempeñar tareas más complicadas, se han ido incrementando los requisitos de memorias de puntos finales de IoT, en especial en el caso de los que ahora desempeñan niveles más altos de computación al borde. Sin embargo, la memoria Flash del microcontrolador en chip está limitada a cerca de 1 megabit (Mb), y muchos puntos finales de IoT de gama alta necesitan muchas veces más memoria.

La solución tradicional ha sido expandir la memoria de programa del microcontrolador con una memoria Flash externa. No obstante, cuando los requisitos de memoria llegan a 8 Mb o más, la mayoría de la memoria del programa termina siendo externa.

En consecuencia, los diseñadores pueden, en muchos casos, beneficiarse de prescindir totalmente de la memoria Flash en chip y, en su lugar, usar un microcontrolador sin Flash, también conocido como sin ROM, junto con una memoria externa Flash octal SPI eXecute-in-place (XiP) de alta velocidad. Esto reduce en gran medida el costo del microcontrolador y prueba el diseño para el futuro al permitir una mayor escalabilidad. El surgimiento de las interfaces de la memoria octal de muy alta velocidad mitiga cualquier duda sobre los tiempos de acceso a la memoria.

Este artículo analiza los microcontroladores sin memoria ROM, las memorias externas y su evolución en una opción viable para los puntos finales de IoT y los sistemas integrados que necesitan grandes cantidades de memoria de programa. A continuación, se muestra cómo aplicar el concepto mediante los microcontroladores sin memoria ROM de NXP Semiconductors y una memoria Flash octal SPI XiP de Adesto Technologies.

Expansión de memoria en el borde de IoT

La mayoría de los puntos finales de IoT de rendimiento bajo a medio usan un microcontrolador para administrar el punto final y almacenan el firmware en la memoria Flash en chip. El firmware se amplía a medida que agrega el código de aplicación adicional, las pilas de comunicaciones IP inalámbricas y el código de seguridad mejorado. La expansión del código puede ocurrir durante el desarrollo y como resultado de las actualizaciones del campo.

Se les pide a algunos de estos puntos finales de IoT desempeñar más funciones informáticas. En lugar de transmitir datos de sensores sin procesar o procesados de manera parcial a través de la red a una computadora central para su procesamiento, estos puntos finales de IoT desempeñan tareas más complejas, que pueden incluir algoritmos de fusión de sensores, interpolación de datos, reconocimiento de patrones o imágenes y la informática de inteligencia artificial (IA), cada día más compleja.

Esto contribuye a que la computadora central solo reciba el resultado del procesamiento local del nodo de IoT en lugar de cada byte de los datos sin procesar del sensor, lo que puede dar lugar a una reducción del tráfico en la red inalámbrica. Debido a que el transmisor de RF puede ser el consumo de energía más importante en un punto final de IoT, la informática de borde a menudo da como resultado una duración de la batería mejorada para los puntos finales alimentados por batería.

Los sistemas que deben actualizarse en el campo afrontan desafíos de memoria adicionales. Los sistemas tradicionales requieren al menos el doble del espacio de la memoria del programa estimado para poder manejar estas actualizaciones. Esto es para manejar tanto la memoria del programa existente como el tamaño de las actualizaciones inalámbricas (OTA). Algunos sistemas pueden requerir tres veces el espacio de la memoria del programa estimado, con la memoria adicional asignada a una imagen de firmware de fábrica de solo lectura. En caso de determinados tipos de fallas del sistema, incluida la detección de pirateo informático o una imagen de firmware dañada, el sistema puede cargar la imagen de firmware de fábrica inicial para recuperar el sistema.

Para algunas aplicaciones, esta expansión de memoria puede superar con rapidez el límite de memoria Flash integrada de 1 Mb, lo que requiere una expansión de memoria externa. Tradicionalmente, la solución ha sido agregar un chip de memoria Flash paralelo externo. Sin embargo, esto tiene la desventaja de usar alrededor de 36 pines externos en el microcontrolador, pines que, de otro modo, podrían usarse para la E/S de la aplicación. Esto desperdicia espacio en la placa de CI y aumenta la probabilidad de interferencia electromagnética (EMI) de la placa.

Expansión de memoria del programa SPI

Además de usar un bus paralelo, también se puede ampliar la memoria del programa mediante la Interfaz periférica serial (SPI). A pesar de que la SPI convencional solo usa una línea de datos para las transmisiones de un solo bit semidúplex, con los años ha crecido para admitir líneas de datos duales y cuádruples, que conllevan un aumento correspondiente en la tasa de producción de datos. Esta tasa de producción ha aumentado hasta un punto en el que se ha vuelto práctico interactuar con una memoria Flash de SPI externa de gran capacidad.

Para las aplicaciones de la memoria del programa, una SPI dual o cuádruple convencional utiliza una configuración de memoria Flash de sombra en la que la memoria de datos Flash externa se copia a una memoria de acceso aleatorio estática (SRAM) que se asigna al espacio de la memoria del programa. Aunque esto tiene la ventaja de poder expandir la memoria del programa con facilidad al tiempo que mejora la velocidad de ejecución por agotar rápido la SRAM, también tiene desventajas importantes. Puesto que la cantidad de SRAM interna es limitada, se accede a la memoria en modo de paginación, ya que la memoria Flash se cambia a la SRAM interna según sea necesario. Este obstáculo se puede sortear al poner más SRAM en chip, pero puesto que la SRAM es uno de los bloques más costosos en cualquier semiconductor, esto tiene la desventaja de aumentar considerablemente el costo del microcontrolador.

Una evolución más reciente de la SPI ha sido XiP. SPI XiP permite que la CPU del microcontrolador ejecute código de firmware fuera de la memoria Flash SPI externa. La velocidad de ejecución del programa se puede mejorar considerablemente al agregar una memoria caché a la interfaz SPI XiP.

La popularidad de SPI XiP ha provocado una expansión reciente de la interfaz con ocho líneas de datos. Esta interfaz octal SPI XiP ha aumentado la tasa de producción hasta un punto en el que es mucho más rápido que agotar la memoria Flash en chip, más rápido que 100 Mb/s.

Revolución de la memoria SPI

Esto ha llevado a una curiosa evolución que es un retroceso de 30 años. Piense en un sistema en el que existe 1 Mb de memoria Flash en chip y 32 Mb de memoria Flash de programa externa a la que se accede mediante una interfaz octal SPI XiP. La memoria del programa en chip es tan mínima que plantea la pregunta: ¿se puede eliminar esa memoria Flash del microcontrolador en chip y seguir siendo un sistema rentable?

Se ha asumido durante mucho tiempo que un sistema de rango medio con un microcontrolador Flash siempre es más rentable en comparación con uno con un microcontrolador sin Flash con una memoria Flash externa. Solo cambió recientemente.

Si se elimina la memoria Flash en chip, por supuesto que se reduce el costo del microcontrolador. Sin embargo, un examen más profundo muestra que si no se necesita la memoria Flash, también se pueden eliminar las características de tecnología de proceso que solo se usan para esta. Esto reduce el costo del proceso de fabricación y reduce en gran medida el costo del microcontrolador, lo que ha provocado un resurgimiento de lo que hace unos 30 años se llamaba el microcontrolador “sin ROM”. Hoy lo llamamos sin Flash.

Reintroducción a los microcontroladores sin Flash

Un microcontrolador de alto rendimiento que puede beneficiarse de la velocidad de la memoria Flash es el MIMXRT1052DVL6B (RT1052) sin Flash de NXP Semiconductors. El RT1052 es miembro de la familia de procesadores i.MX RT1050 de NXP y se basa en Arm®Cortex®-M7 de 600 megahercios (MHz) con 32 KB de caché de instrucciones y 32 KB de caché de datos. La velocidad de reloj de 600 MHz se logra al quitar la memoria Flash y mediante una tecnología de proceso CMOS de alta velocidad que no está limitada por la memoria Flash interna. El RT1052 cuenta con una gran cantidad de SRAM de 512 kilobytes (KB) que se puede particionar para el uso de la memoria de datos o el programa.

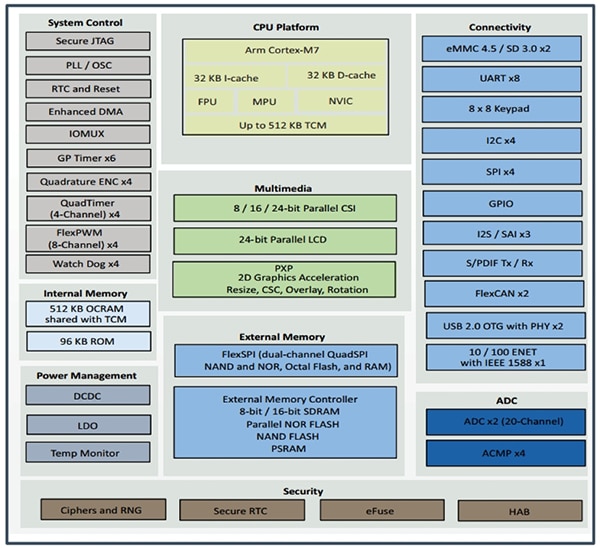

El microcontrolador tiene una amplia variedad de periféricos de alta gama que incluyen una interfaz LCD, una interfaz del sensor de cámara digital (CSI) y una canalización de procesamiento de píxeles (PXP) para soporte de la cámara de alta gama, una interfaz SPDIF para audio digital, dos interfaces USB OTG, dos Interfaces de tarjetas de memoria Flash eMMC/SD, dos convertidores analógico al digital (ADC) de 20 canales y un módulo de cifrado. Se puede observar una lista completa de periféricos en el diagrama de bloque (Figura 1).

Figura 1: El NXP RT1052 tiene una amplia variedad de periféricos de alta gama, que incluyen una interfaz en serie SPI XiP y soporte para el cifrado de datos. (Fuente de la imagen: NXP)

Figura 1: El NXP RT1052 tiene una amplia variedad de periféricos de alta gama, que incluyen una interfaz en serie SPI XiP y soporte para el cifrado de datos. (Fuente de la imagen: NXP)

Otra opción es el NXP MIMXRT1051DVL6B (RT1051). Tiene las mismas características del RT1052, menos la interfaz LCD, CSI y PXP.

El RT1052 tiene una interfaz FlexSPI, que puede ejecutar el código mediante las interfaces Flash SPI XiP duales, cuádruples u octales. Para mayor seguridad del firmware, el microcontrolador admite la memoria del programa encriptado sobre SPI XiP. Un buen ejemplo es el ATXP032-CCUE-T de Adesto Technologies.

Operación de la memoria Flash XiP moderna

El ATXP032-CCUE-T de Adesto Technologies es una memoria Flash octal de 32 Mb que admite transferencias de datos de hasta 266 megabytes (MB) por segundo en modo de velocidad de transferencia dual (DTR) y octal, mucho más rápido que la memoria Flash del microcontrolador en chip. Requiere un solo suministro de 1.8 voltios y tiene una corriente de reserva en modo octal típica de 35 microamperios (µA). Admite un reloj SPI máximo de 133 MHz.

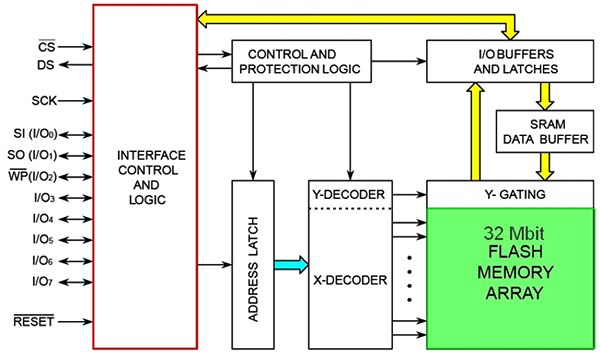

Figura 2: La memoria Flash ATXP032-CCUE-T de Adesto utiliza un SPI octal, E/S0 a E/S7 para interactuar con un microcontrolador. Un búfer de datos de escritura SRAM mejora el rendimiento de las operaciones de escritura en la memoria Flash. (Fuente de la imagen: Adesto Technologies)

Figura 2: La memoria Flash ATXP032-CCUE-T de Adesto utiliza un SPI octal, E/S0 a E/S7 para interactuar con un microcontrolador. Un búfer de datos de escritura SRAM mejora el rendimiento de las operaciones de escritura en la memoria Flash. (Fuente de la imagen: Adesto Technologies)

Durante una lectura de memoria Flash activa, el consumo de corriente del ATXP32 es de 142 µA/MHz más 1 miliamperio (mA) de sobrecarga (típico). Solo consume 19.9 mA con su velocidad máxima de reloj SPI de 133 MHz en modo octal.

El ATXP032-CCUE-T también admite los modos SPI estándar 0 y 3, así como el modo SPI cuádruple. Un registro de seguridad de 256 bytes tiene un identificador único programado de fábrica de 128 bytes, así como 128 bytes de memoria programable una sola vez (OTP) que se puede usar para almacenar información del dispositivo, como una dirección de control de acceso al medio (MAC) Ethernet o una clave de seguridad.

Vale la pena mencionar la disposición de la memoria de ATXP032-CCUE-T. Está dividida en cuatro paneles de 8 Mb cada uno. La lógica interna se configura para que un microcontrolador host pueda ejecutar el código fuera de un panel al tiempo que programa o borra otro. La operación es transparente para el microcontrolador host y no requiere opciones de configuración especiales.

El ATXP032-CCUE-T también cuenta con tres registros de estado y control para configurar los parámetros operativos del dispositivo, como el modo de bajo consumo, habilitar o deshabilitar el modo DTR y configurar los modos SPI octal o cuádruple estándar (el SPI estándar es la opción predeterminada). La lectura de los registros de estado puede indicar el estado de un programa o borrar la operación, el estado de bajo consumo y si la memoria está protegida contra escritura.

Colocar los microcontroladores sin Flash y XiP externo juntos

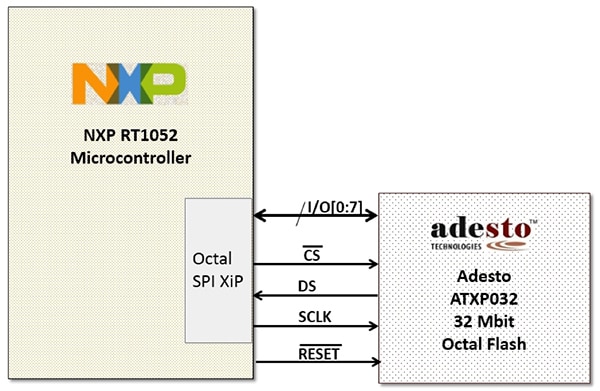

Poner el RT1052 y el ATXP032-CCUE-T juntos es sencillo (Figura 3). Al encenderlo, el RT1052 comienza a ejecutar el código desde los 96 KB de la ROM de arranque en chip. La ROM de arranque lee el estado de 14 pines de configuración del modo de arranque que selecciona cuál de las muchas interfaces de memoria externa RT1052 se utilizará para la memoria del programa. Las opciones incluyen una tarjeta de memoria eMMC externa, una tarjeta micro SD, una interfaz paralela externa convencional o el SPI XiP (en este caso, el ATXP032-CCUE-T de Adesto).

Figura 3: El microcontrolador sin Flash NXP RT1052 tiene una interfaz octal SPI XiP que puede conectarse fácilmente al ATXP032-CCUE-T de Adesto. La operación de la interfaz octal SPI XiP es transparente para el núcleo Arm. (Fuente de la imagen: DigiKey)

Figura 3: El microcontrolador sin Flash NXP RT1052 tiene una interfaz octal SPI XiP que puede conectarse fácilmente al ATXP032-CCUE-T de Adesto. La operación de la interfaz octal SPI XiP es transparente para el núcleo Arm. (Fuente de la imagen: DigiKey)

Las opciones de arranque RT1052 también incluyen la descarga del código desde el USB OTG o un UART que se ejecutará desde SRAM. Las opciones del modo de arranque también se pueden configurar durante la fabricación al soplar los fusibles internos dentro del RT1052 en lugar de usar los pines de configuración del modo de arranque. Una vez que se habilita la interfaz octal SPI XiP para la ejecución de la memoria del programa mediante la ROM de arranque del RT1052, la ejecución del programa es inmediata. El núcleo Arm ejecuta el firmware del ATXP032-CCUE-T de Adesto de la misma manera que desde un dispositivo de memoria Flash paralelo externo o interno.

Debido a las transferencias de datos de alta velocidad que se emplean, la memoria Flash octal en serie debe colocarse en la placa de CI lo más cerca posible del puerto SPI XiP octal del microcontrolador. Para reducir las interferencias, ninguno de los trazados de CI debe tener más de 120 milímetros (mm). La señal del reloj debe estar a una distancia de al menos tres veces el ancho de los trazados de la placa de CI lejos de otras señales para evitar interferencias. Las señales de datos bidireccionales E/S [0:7] deben estar todas a una distancia de 10 mm entre sí para evitar sesgos.

Conclusión

Los puntos finales de IoT tienen requisitos de memoria cada vez mayores debido a las tendencias de la informática de borde, la necesidad de actualizaciones OTA y a las necesidades de escalabilidad de memoria asociada. En un cierto punto, los diseñadores de estos dispositivos de punto final pueden encontrar una opción para usar un microcontrolador sin Flash que convenga analizar.

Como puede observarse, los avances en los microcontroladores sin Flash, las interfaces de alta velocidad y las memorias Flash octales SPI XiP brindan a los desarrolladores la opción de crear puntos finales de IoT de alto rendimiento y rentables o sistemas integrados en lugar de usar enfoques tradicionales de microcontroladores basados en Flash.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.