Los fundamentos de los sintetizadores de frecuencia de bucle bloqueado de fase

Colaboración de Editores de DigiKey de América del Norte

2021-02-03

El aumento de la velocidad de los datos en los buses de comunicaciones en serie de alta velocidad requiere relojes de sistema con frecuencias más altas, mayor estabilidad, mayor resolución de frecuencia y mayor pureza de señal. Los sintetizadores digitales directos ofrecen estas características, pero solo a frecuencias inferiores a 2 ó 3 gigahercios (GHz). Se necesita una solución para frecuencias de hasta decenas de gigahercios.

Esta solución comienza con sintetizadores de frecuencia analógicos basados en bucles de bloqueo de fase (PLL) que generan frecuencias de reloj de hasta 30 GHz. Entonces, los sintetizadores N enteros (que multiplican la frecuencia de referencia por un valor entero) y los sintetizadores N fraccionarios (que multiplican la frecuencia de referencia por valores fraccionarios no enteros) emplean técnicas especiales que minimizan el ruido de fase y otras impurezas similares de la señal.

Este artículo describe el diseño de sintetizadores de frecuencia tanto N enteros como fraccionarios utilizando dispositivos de ejemplo de Analog Devices. El artículo también destaca las innovaciones que permiten utilizar estos dispositivos para enlaces de datos en serie de alta velocidad, así como para radares de frecuencia ágil.

Sintetizadores de bucle cerrado de fase de número entero

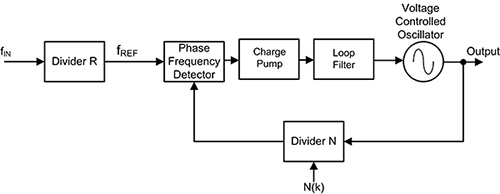

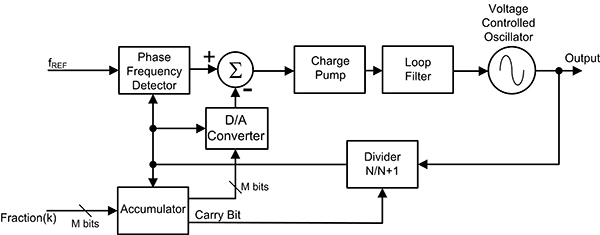

Los circuitos PLL se utilizan para el control de frecuencia y de fase. Pueden configurarse como fuentes de reloj, multiplicadores de frecuencia, demoduladores, generadores de seguimiento o circuitos de recuperación de reloj. Cada una de estas aplicaciones exige características diferentes, pero todas utilizan el mismo concepto básico de circuito. La figura 1 muestra un diagrama de bloques de un PLL básico configurado como multiplicador de frecuencia.

Figura 1: Diagrama de bloques de un sintetizador de frecuencia de bucle cerrado de fase N clásico. (Fuente de la imagen: DigiKey)

Figura 1: Diagrama de bloques de un sintetizador de frecuencia de bucle cerrado de fase N clásico. (Fuente de la imagen: DigiKey)

El funcionamiento de este circuito es el típico de todos los bucles de bloqueo de fase. Es básicamente un sistema de control de retroalimentación que controla la fase de un oscilador controlado por tensión (VCO). La señal de entrada se aplica a un divisor de preescalado, que divide la frecuencia de entrada por un factor R. La salida del preescalado es la frecuencia de referencia, que constituye una entrada de un detector de frecuencia de fase (PFD).

La otra entrada del PFD es una señal de retroalimentación de la salida de un contador de división por N. Normalmente, si el PLL está bloqueado, las frecuencias de ambas señales serán casi iguales. La salida del detector de fase es un voltaje proporcional a la diferencia de fase entre las dos entradas. Si el bucle se desbloquea, como ocurre en el arranque o si hay un gran desplazamiento instantáneo en la frecuencia de la entrada, entonces el detector de frecuencia de fase opera para dirigir la frecuencia de funcionamiento del PLL al ajuste deseado. Cuando se alcanza esa frecuencia, el PFD vuelve al modo de detector de fase y tiene una salida proporcional a la diferencia de fase entre la frecuencia de referencia y la señal de retroalimentación.

El detector de frecuencia de fase acciona una bomba de carga, que es una fuente de corriente conmutada bipolar. Esto significa que puede emitir pulsos de corriente positivos y negativos en el filtro de bucle del PLL.

El filtro de bucle suaviza la señal de error de fase y también determina las características dinámicas del PLL. La señal filtrada controla el VCO. Obsérvese que la salida del VCO está a una frecuencia que es N veces la entrada suministrada a la entrada de referencia de frecuencia al detector de fase-frecuencia y es N/R veces la entrada de frecuencia. Esta señal de salida se envía de vuelta al detector de fase a través de la división por el contador N.

Normalmente, el filtro de bucle está diseñado para que coincida con las características requeridas por la aplicación del PLL. Si el PLL va a adquirir y rastrear una señal, el ancho de banda del filtro de bucle será mayor que si esperara una frecuencia de entrada fija. El rango de frecuencias que el PLL aceptará y bloqueará se denomina "rango de captura" Una vez que el PLL está bloqueado y sigue una señal, el rango de frecuencias que seguirá el PLL se denomina "rango de seguimiento" En general, el rango de seguimiento es mayor que el rango de captura. El filtro del bucle PLL también determina la rapidez con la que la frecuencia de la señal puede cambiar y seguir manteniendo el bloqueo, es decir, la máxima velocidad de giro. Cuanto más estrecho sea el ancho de banda del filtro de bucle, menor será el error de fase alcanzable. Esto se produce a expensas de una respuesta más lenta y un rango de captura reducido. Los PLL utilizados en las aplicaciones de reloj funcionan principalmente a frecuencias fijas. En general, el ancho de banda del filtro de bucle debe ser mucho menor que la frecuencia de referencia.

Como la frecuencia de salida del PLL es un múltiplo entero de la frecuencia de referencia, su resolución de frecuencia es igual a la frecuencia de referencia. Para obtener una resolución de frecuencia más fina es necesario disminuir la frecuencia de referencia, lo que se hace con el contador de pre-escala R.

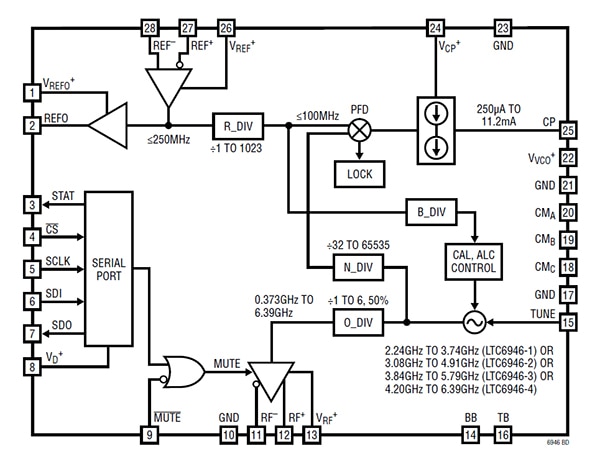

Un ejemplo comercial de sintetizador de frecuencias de N entero es el LTC6946IUFD-3#PBF de Analog Devices, un sintetizador de bajo ruido de 0.64 a 5.790 GHz con un VCO integrado y un excelente rendimiento contra espurias (Figura 2). Forma parte de una familia de cuatro circuitos integrados sintetizadores, cada uno de ellos con un rango de frecuencias diferente, cubriendo un rango total de 0.373 a 6.390 GHz.

Figura 2: Diagrama de bloques del sintetizador de frecuencias de N entero LTC6946IUFD-3#PBF de Analog Devices con VCO integrado. (Fuente de la imagen: Analog Devices)

Figura 2: Diagrama de bloques del sintetizador de frecuencias de N entero LTC6946IUFD-3#PBF de Analog Devices con VCO integrado. (Fuente de la imagen: Analog Devices)

Este sintetizador requiere un filtro de bucle externo suministrado por el usuario, que puede ser optimizado para la aplicación específica. Hay un divisor interno de contador de pre-escala con un rango de división de 1 a 1023. El divisor de bucle tiene un rango de 32 a 65535. La corriente de la bomba de carga es ajustable desde 250 microamperios (mA) hasta 11.2 miliamperios (mA) para adaptarse a los requisitos del filtro de bucle.

Sintetizadores de bucle cerrado de fase N fraccional

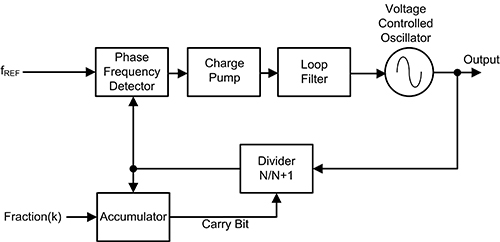

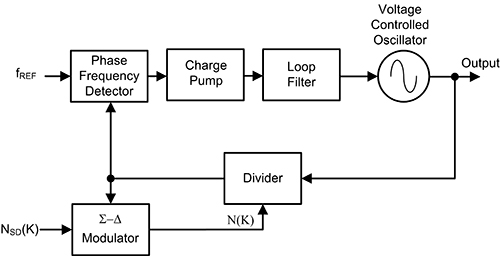

La resolución de frecuencia del sintetizador PLL puede mejorarse reduciendo el tamaño del paso a valores inferiores a los enteros, es decir, haciendo pasos fraccionados en el divisor del bucle (N). Esto se consigue variando dinámicamente o "dithering" el valor de la cuenta atrás. Esto significa que el ajuste del divisor mantiene el valor N para un número fijo de ciclos de la frecuencia de salida del PLL y es periódicamente escalonado a un valor diferente, como N+1. Por ejemplo, si el ajuste del divisor es 4 para tres periodos de referencia y 5 para el cuarto ciclo de referencia, entonces la cuenta atrás efectiva es de 4.25. Una forma de conseguirlo es utilizar un acumulador, como se muestra en la figura 3.

Figura 3: El diagrama de bloques de un sintetizador PLL de N fraccional que utiliza un acumulador para modular la cuenta del divisor. (Fuente de la imagen: DigiKey)

Figura 3: El diagrama de bloques de un sintetizador PLL de N fraccional que utiliza un acumulador para modular la cuenta del divisor. (Fuente de la imagen: DigiKey)

El acumulador cuenta los pulsos de salida del divisor, y cada M, donde M es el módulo del acumulador, emite un bit de acarreo que cambia la entrada del divisor. La figura 4 continúa el ejemplo de establecer un ajuste de divisor fraccionario de 4.25.

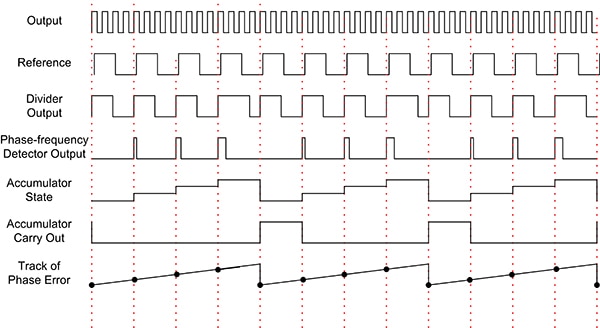

Figura 4: Diagrama de temporización de un sintetizador de N fraccionario que utiliza un acumulador. (Fuente de la imagen: DigiKey)

Figura 4: Diagrama de temporización de un sintetizador de N fraccionario que utiliza un acumulador. (Fuente de la imagen: DigiKey)

El acumulador es accionado por la salida dividida y cuenta en módulo cuatro, es decir, M es igual a cuatro. Cada cuatro impulsos genera una salida de acarreo, que incrementa en uno la cuenta del divisor. El acumulador se reinicia y comienza a contar de nuevo. El aumento del ajuste del divisor desplaza la frecuencia de salida, lo que provoca un error de desfase acumulado. La pista del error de fase muestra el valor del pulso en función del tiempo.

El ajuste del divisor medio es de 4.25, pero la salida del sintetizador está modulada en fase, lo que provoca tonos espurios en la salida. Al observar el estado del acumulador es evidente que sigue el error de fase. Esto se puede utilizar para eliminar la modulación como se muestra en la Figura 5.

Figura 5: Utilización del estado del acumulador convertido en D/A para cancelar la modulación de fase debida al dithering fraccional N. (Fuente de la imagen: DigiKey)

Figura 5: Utilización del estado del acumulador convertido en D/A para cancelar la modulación de fase debida al dithering fraccional N. (Fuente de la imagen: DigiKey)

El estado del acumulador se convierte en analógico mediante un convertidor de digital a analógico (D/A) y se escala y se resta de la salida del detector de fase-frecuencia para cancelar la modulación de fase debida al dithering de N fraccional. Esto debe hacerse con mucho cuidado; si la señal de corrección no coincide exactamente con el error de fase, se producirán tonos espurios en la salida.

Introduzca el modulador sigma-delta

La periodicidad en el acumulador es la causa de las salidas espurias del sintetizador. Si se sustituye el acumulador por un modulador sigma-delta, se pueden aplicar técnicas digitales para modular el recuento del divisor de forma que se minimicen las respuestas espurias y el ruido. Esta sustitución se muestra en la figura 6.

Figura 6: La sustitución del acumulador por un modulador sigma-delta permite aplicar técnicas digitales para variar el recuento del divisor con el fin de reducir las respuestas espurias. (Fuente de la imagen: DigiKey)

Figura 6: La sustitución del acumulador por un modulador sigma-delta permite aplicar técnicas digitales para variar el recuento del divisor con el fin de reducir las respuestas espurias. (Fuente de la imagen: DigiKey)

Hay realmente dos técnicas digitales comunes que se emplean en la topología de modulación sigma-delta. La primera consiste en aumentar el número de recuentos del divisor N en un rango más amplio de valores, de forma que el factor de división medio produzca el valor del divisor fraccionario deseado. Esto reducirá los espolones fraccionados primarios. El sintetizador basado en acumuladores varía la cuenta entre dos estados. Se trata de un método de modulación de primer orden. Un PLL fraccional sigma-delta de enésimo orden modula el contador N entre 2n valores diferentes. Por ejemplo, un modulador de tercer orden alternaría entre ocho valores diferentes de divisor, y un modulador de cuarto orden alternaría entre 16 valores diferentes de divisor.

La segunda técnica digital -también denominada dithering- consiste en aleatorizar la secuencia 2N para que sea pseudoaleatoria. Mientras se mantiene una relación media del divisor fraccional, convierte los espolones fraccionales en ruido aleatorio con forma de tal manera que puede ser filtrado por el PLL.

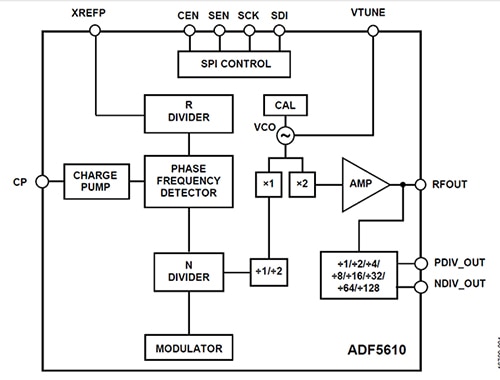

Una versión comercial de un sintetizador N fraccional sigma-delta es el ADF5610BCCZ de Analog Devices, un sintetizador N fraccional de bajo ruido de 0.57 megahercios (MHz) a 14.6 GHz con un VCO integrado (Figura 7).

Figura 7: Diagrama de bloques ADF5610BCCZ de Analog Devices que admite configuraciones de sintetizador fraccionario N o entero. (Fuente de la imagen: Analog Devices).

Figura 7: Diagrama de bloques ADF5610BCCZ de Analog Devices que admite configuraciones de sintetizador fraccionario N o entero. (Fuente de la imagen: Analog Devices).

El ADF5610 requiere un oscilador de referencia externo y un filtro de bucle. Tiene un VCO integrado con una frecuencia fundamental de 3650 MHz a 7300 MHz. Estas frecuencias se duplican internamente y se enrutan en el pin de RFOUT. Hay una salida diferencial que permite dividir la frecuencia VCO duplicada por factores de 1, 2, 4, 8, 16, 32, 64 o 128, lo que permite generar frecuencias de salida de RF tan bajas como 57 MHz.

El ADF5610 utiliza un modulador sigma-delta avanzado con un módulo fraccionario de 24 bits que consigue niveles de espurias excepcionalmente bajos. Como en todos los sintetizadores que utilizan un modulador sigma-delta, este dispositivo utiliza técnicas de procesamiento de señales digitales para encontrar la relación media del divisor fraccionario deseada. Este proceso, sincronizado a la tasa de PFD, produce un ruido de modulación de salida llamado ruido de cuantificación con una respuesta de frecuencia de paso alta. El filtro de bucle de paso bajo externo se utiliza para filtrar este ruido de cuantificación hasta un nivel inferior al ruido de fase del VCO, evitando así que el ruido contribuya al ruido de fase global del sistema.

El ADF5610 también incluye un modo de frecuencia exacta para un error de frecuencia de 0 hertz (Hz). Este modo es capaz de generar frecuencias exactas entre pasos adyacentes de límites enteros N mientras sigue utilizando el módulo completo del acumulador de fase de 24 bits. Consigue pasos de frecuencia exactos con una alta tasa de comparación del detector de fase, lo que permite al PLL mantener un excelente ruido de fase y rendimiento de espurias en este modo.

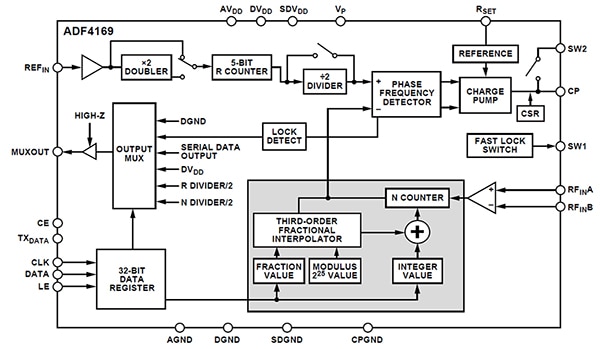

El ADF4169CCPZ-RL7 de Analog Devices es otro sintetizador PLL que puede configurarse como un dispositivo N entero o N fraccionario. Funciona con un ancho de banda de RF de hasta 13.5 GHz con modulación y generación de formas de onda. Utiliza una entrada de frecuencia de referencia externa, un VCO y un filtro de bucle. Dispone de un modulador sigma-delta de tercer orden para la síntesis N fraccional que puede desactivarse, lo que permite que el dispositivo funcione en modo N entero (Figura 8).

Figura 8: El ADF4169CCPZ-RL7 de Analog Devices utiliza un modulador sigma-delta de tercer orden. (Fuente de la imagen: Analog Devices)

Figura 8: El ADF4169CCPZ-RL7 de Analog Devices utiliza un modulador sigma-delta de tercer orden. (Fuente de la imagen: Analog Devices)

El sintetizador ADF4158WCCPZ-RL7 está pensado para su uso en radares de onda continua de frecuencia modulada (FMCW). Es capaz de realizar varios tipos de formas de onda moduladas en el dominio de la frecuencia, incluyendo dientes de sierra y rampas triangulares. Esta es una característica especial que es necesaria en las aplicaciones de radar.

Conclusión:

El aumento de la velocidad de los datos en los buses de comunicaciones serie de alta velocidad obliga a los diseñadores a ir más allá de los sintetizadores digitales directos -que funcionan mejor por debajo de 3 GHz- para encontrar soluciones de reloj de sistema. Los sintetizadores de frecuencia basados en PLL que utilizan topologías de N enteros y N fraccionarios proporcionan señales estables y de bajo ruido para aplicaciones de reloj de alta frecuencia, comunicaciones de datos en serie y radares para frecuencias de hasta decenas de gigahercios.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.