Cumplir con diversos requisitos funcionales y de seguridad con los procesadores multinúcleo

Colaboración de Editores de DigiKey de América del Norte

2020-10-01

Se espera que las aplicaciones automovilísticas, industriales, robóticas, de control de edificios y otras aplicaciones de sistemas empotrados críticos asuman cargas de trabajo más diversas que van desde el monitoreo de baja potencia en tiempo real hasta aplicaciones multimedia de alto nivel con pantallas gráficas multipantalla para interfaces hombre-máquina (HMI). Al mismo tiempo que cumplen estos amplios requisitos funcionales, también deben ser capaces de soportar estrictas normas de seguridad, reducir el costo y la huella, y optimizar el equilibrio entre potencia y rendimiento.

Para cumplir con estos requisitos, a veces contradictorios, los desarrolladores se han visto obligados hasta la fecha a sacrificar la capacidad funcional o a complicar el diseño y la fabricación con los dispositivos adicionales necesarios para apoyar los requisitos específicos de los gráficos, la seguridad y la protección, entre otros. Lo que los desarrolladores realmente necesitan es una solución única capaz de soportar una amplia gama de productos que cumplan con estos requisitos en una amplia gama de aplicaciones de sistemas empotrados críticos.

Este artículo describe rápidamente la evolución del diseño de sistemas empotrados críticos. A continuación, se mostrará cómo los procesadores de aplicaciones multinúcleo, diseñados específicamente por NXP Semiconductores para apoyar una lista en rápida expansión de requisitos tanto de funcionalidad amplia como de capacidades certificables de seguridad, pueden utilizarse para abordar los desafíos de los desarrolladores.

La evolución de las consideraciones de diseño de los sistemas empotrados

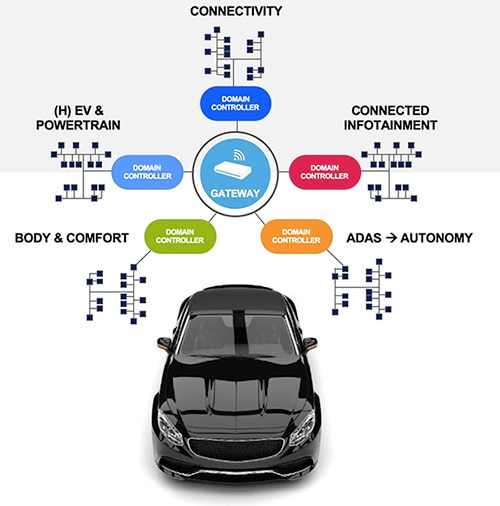

El papel tradicional de los dispositivos incorporados en apoyo de un conjunto limitado de funciones del sistema ha sido sustituido en gran medida por la demanda de dispositivos que ofrezcan amplias capacidades. En las aplicaciones industriales, por ejemplo, la necesidad de mejorar las capacidades de HMI en herramientas y equipos inteligentes exige procesadores capaces de ofrecer gráficos optimizados y, al mismo tiempo, cumplir con los requisitos industriales más tradicionales en tiempo real. Del mismo modo, la tendencia de las aplicaciones de automoción hacia arquitecturas jerárquicas que comprenden grupos de dominio funcional y pasarelas impulsa la necesidad de contar con procesadores plenamente capaces de cumplir esos requisitos (figura 1).

Figura 1: La tendencia hacia arquitecturas de sistemas automotrices más jerárquicas ha creado la necesidad de soluciones de procesadores más integradas y escalables. (Fuente de la imagen: NXP Semiconductors)

Figura 1: La tendencia hacia arquitecturas de sistemas automotrices más jerárquicas ha creado la necesidad de soluciones de procesadores más integradas y escalables. (Fuente de la imagen: NXP Semiconductors)

Dentro de cada ámbito funcional, la demanda de capacidades más sofisticadas sigue elevando el umbral de rendimiento y de capacidades integradas. Por ejemplo, la aparición de pantallas de aviso exige soluciones capaces de asegurar la entrega continua de información gráfica vital a los conductores. Junto con estas pantallas de última generación, la creciente necesidad de mejorar la conciencia del conductor añade requisitos adicionales para las interfaces de las cámaras y la ejecución de alto rendimiento del software de reconocimiento avanzado capaz de proporcionar la detección de la somnolencia.

A medida que las aplicaciones continúan evolucionando, la necesidad de soluciones altamente integradas y escalables se hace más urgente para satisfacer los requisitos cada vez más diversos y, al mismo tiempo, reducir al mínimo la huella del diseño, el costo y la complejidad. Al usar la familia de procesadores de aplicación i.MX 8 de NXP, los desarrolladores pueden aprovechar una plataforma compatible de procesadores con la gama de capacidades y el rendimiento necesarios para apoyar una amplia gama de requisitos de aplicación. Dentro de la familia i.MX 8, la serie i.MX 8X de NXP se ocupa de las necesidades emergentes de procesadores certificables de seguridad que se requieren en aplicaciones automovilísticas e industriales de gama media.

La arquitectura multinúcleo gestiona diversas cargas de trabajo

Una de las dificultades a las que se enfrentan los desarrolladores para implementar dispositivos para aplicaciones automotrices e industriales es la gran amplitud de los requisitos. En los casos en que los desarrolladores podrían esperar tratar con cargas de trabajo de procesamiento de aplicaciones en tiempo real o de alto nivel, la demanda de subsistemas inteligentes ha fusionado estos tipos de computación significativamente diferentes. Cada vez más, los desarrolladores necesitan soluciones capaces de ofrecer tanto una respuesta fiable en tiempo real como una ejecución de aplicaciones de alto rendimiento, a la vez que apoyan los requisitos de seguridad funcional.

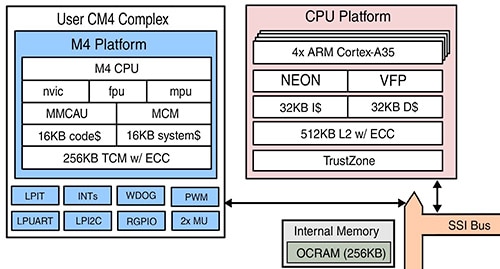

Diseñados para ofrecer capacidades en tiempo real, procesamiento de alto rendimiento y bajo consumo de energía, los procesadores de la serie i.MX 8X de NXP aprovechan al máximo una sofisticada arquitectura de unidad central de procesamiento (CPU) multinúcleo para gestionar diversas cargas de trabajo computacional (Figura 2).

Figura 2: La serie i.MX 8X de NXP utiliza una arquitectura multinúcleo que comprende un procesador integradoArm Cortex-M4 (CM4) y múltiples procesadores de aplicación Arm Cortex-A35 para soportar cargas de trabajo de software mixtas. (Fuente de la imagen: NXP Semiconductors)

Figura 2: La serie i.MX 8X de NXP utiliza una arquitectura multinúcleo que comprende un procesador integradoArm Cortex-M4 (CM4) y múltiples procesadores de aplicación Arm Cortex-A35 para soportar cargas de trabajo de software mixtas. (Fuente de la imagen: NXP Semiconductors)

Para las tareas de procesamiento en tiempo real de propósito general, los dispositivos i.MX 8X incluyen un procesador Arm Cortex-M4 (CM4) con unidad de punto flotante (FPU), unidad de protección de memoria (MPU), unidad de aceleración criptográfica mapeada en memoria (MMCAU) y módulo de control misceláneo (MCM). Para soportar periféricos externos como sensores y actuadores, este complejo CM4 de usuario combina un controlador de interrupción vectorial anidado (NVIC) con un conjunto completo de interfaces y módulos, incluyendo un temporizador de interrupción periódica de baja potencia (LPIT), modulación de ancho de pulso (PWM), y otras funciones comúnmente requeridas en aplicaciones automotrices e industriales. Un par de memorias caché y una memoria estrechamente acoplada (TCM) con capacidad de código de corrección de errores (ECC) ayuda a minimizar el acceso a la memoria externa, a acelerar la ejecución y a tratar los errores de la memoria.

Para una rápida ejecución de las cargas de trabajo de aplicación, la plataforma de la CPU comprende múltiples procesadores de aplicación (AP) Arm Cortex-A35 de bajo consumo, dos AP en los procesadores 8DualXPlus, como el MIMX8UX6AVLFZAC, y cuatro AP en los procesadores 8QuadXPlus, como el MIMX8QX6AVLFZAC. Junto con la caché dedicada de instrucciones (I$) y datos (D$), la plataforma de la CPU incluye una caché compartida de 512 kilobytes (Kbyte) de nivel 2 (L2) con ECC.

Los núcleos Arm Cortex-A35 de la arquitectura proporcionan tanto compatibilidad de software como escalabilidad de rendimiento, soportando tanto la compatibilidad hacia atrás de 32 bits como el rendimiento de 64 bits. Para acelerar aún más la ejecución de los algoritmos de cálculo intensivo, como el procesamiento de señales y el aprendizaje automático, los procesadores Arm Cortex-A35 proporcionan procesamiento de punto flotante vectorial (VFP) y extensiones de la arquitectura de datos múltiples de instrucción única (SIMD) Neon de Arm. Para acelerar la ejecución del software para el procesamiento de imágenes, la visión por computadora y el aprendizaje por máquina, la biblioteca Compute Library ofrece funciones optimizadas para las arquitecturas del procesador Arm y de la unidad de procesamiento gráfico (GPU), y la biblioteca Ne10 C de código abierto proporciona funciones optimizadas para el Arm para operaciones de cálculo intensivo.

Los motores dedicados descargan las CPU primarias

Además del complejo CM4 del usuario y la plataforma de CPU multinúcleo Arm Cortex-A35, la arquitectura proporciona motores dedicados adicionales para aplicaciones multimedia. Junto con un procesador de señales digitales (DSP) para el procesamiento de audio y códecs de voz, la arquitectura integra tanto una GPU como una unidad de procesamiento de video (VPU). La GPU del dispositivo es compatible con las librerías gráficas estándar, acelerando las operaciones mediante cuatro vectores de punto flotante (vec4) de cuatro componentes separados con 16 unidades de ejecución y un motor de bit blit de dos dimensiones de alto rendimiento. La VPU maneja los formatos de video más populares, acelerando la decodificación hasta 4Kp30 (progresiva, 30 Hz) y la codificación hasta 1080p30. A su vez, el bloque controlador de pantalla dedicado del chip puede dirigir la salida de los gráficos hasta tres pantallas independientes.

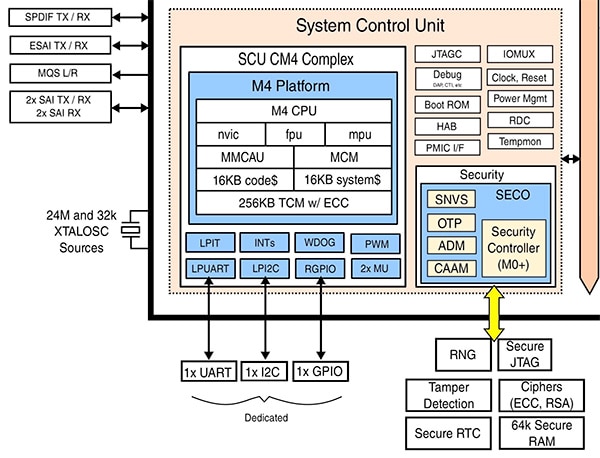

Para maximizar aún más el rendimiento, la arquitectura i.MX 8X también integra núcleos de procesador adicionales diseñados para liberar a las plataformas de CPU primarias de la carga de procesamiento adicional en la que normalmente se incurre al ejecutar los servicios de gestión y seguridad del sistema. Para la gestión del sistema, la unidad de control del sistema (SCU) de la arquitectura integra un complejo CM4 que coincide con el complejo CM4 del usuario, pero sigue dedicado completamente a las operaciones de la SCU y no está disponible para su uso por parte de los desarrolladores (Figura 3).

Figura 3: Integrado en lo profundo de los procesadores i.MX 8X de NXP y no disponible para los desarrolladores, el SCU utiliza un subsistema dedicado de Arm Cortex-M4 (CM4) para descargar las tareas de administración del sistema de los procesadores principales del dispositivo. (Fuente de la imagen: NXP Semiconductors)

Figura 3: Integrado en lo profundo de los procesadores i.MX 8X de NXP y no disponible para los desarrolladores, el SCU utiliza un subsistema dedicado de Arm Cortex-M4 (CM4) para descargar las tareas de administración del sistema de los procesadores principales del dispositivo. (Fuente de la imagen: NXP Semiconductors)

Junto con la gestión de la energía, el reloj y otras funciones internas, la SCU controla la multiplexación de pines y la fuerza de accionamiento de los canales de entrada/salida (E/S) en el funcionamiento normal. De hecho, el complejo CM4 del usuario y los AP Arm Cortex-A35 no pueden acceder directamente a estas diversas capacidades de hardware de bajo nivel. En cambio, la SCU sirve para abstraer estas capacidades, por lo que el software que se ejecuta en el CM4 o AP del usuario simplemente necesita llamar a las funciones de la interfaz de programación de aplicaciones (API) del firmware de la SCU para realizar funciones como la de apagar los dominios de energía innecesarios. Si ese dominio power domain se comparte con otro procesador, por ejemplo, la SCU simplemente reconoce la solicitud de apagado, pero mantiene el dominio encendido hasta que ese otro procesador emita también una solicitud de apagado.

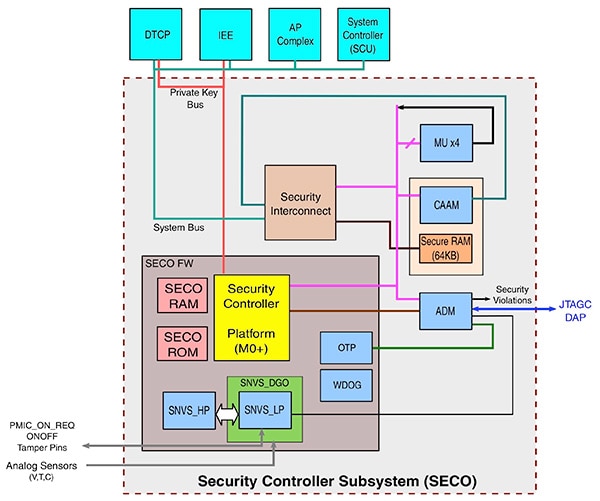

Para gestionar el amplio soporte de seguridad del dispositivo i.MX 8X, otro procesador dedicado entra en juego en el subsistema del controlador de seguridad del dispositivo (SECO). Dentro del subsistema SECO, un procesador integrado de baja potencia Arm Cortex-M0+ ejecuta un firmware que soporta capacidades de seguridad basadas en hardware, incluyendo un acceso privado al bus para claves seguras, memoria programable de una sola vez (OTP) para el almacenamiento seguro de claves, y almacenamiento seguro no volátil (SNVS) para datos privados adicionales o claves efímeras (Figura 4).

Figura 4: Dentro del subsistema del controlador de seguridad (SECO) i.MX 8X de NXP, un procesador Arm Cortex-M0+ de baja potencia dedicada gestiona las operaciones de seguridad, recurriendo a un bus de clave privada y a múltiples módulos de hardware para el almacenamiento seguro, la aceleración de la criptografía y el acceso de depuración autenticado. (Fuente de la imagen: NXP Semiconductors)

Figura 4: Dentro del subsistema del controlador de seguridad (SECO) i.MX 8X de NXP, un procesador Arm Cortex-M0+ de baja potencia dedicada gestiona las operaciones de seguridad, recurriendo a un bus de clave privada y a múltiples módulos de hardware para el almacenamiento seguro, la aceleración de la criptografía y el acceso de depuración autenticado. (Fuente de la imagen: NXP Semiconductors)

Más allá de estos mecanismos de seguridad básicos, el subsistema SECO coordina las operaciones de seguridad para la detección de manipulaciones y la depuración segura mediada por su Módulo de Depuración Autenticado (ADM). Para una ejecución segura, el módulo de seguridad del hardware del Módulo de Aceleración y Garantía de Criptografía (CAAM) integrado soporta un conjunto completo de algoritmos de seguridad que incluye criptografía simétrica y asimétrica, funciones hash y un generador de números aleatorios (RNG).

En el funcionamiento normal, las unidades de procesamiento de dispositivos, incluyendo la SCU, los AP y el acelerador de Protección del Contenido del Transporte Digital (DTCP), utilizan la interconexión de seguridad de la SECO para acceder a la funcionalidad de la CAAM a través del bus del sistema. Aparte del acceso a través de la funcionalidad de acceso directo a la memoria CAAM (DMA), el procesador dedicado Cortex-M0+ del SECO no puede acceder al bus del sistema. En su lugar, utiliza conexiones internas protegidas para acceder a los periféricos, a la memoria de acceso aleatorio seguro (RAM) y a la memoria de sólo lectura (ROM), y a su bus especial de claves privadas.

Junto con su uso del acelerador DTCP, este bus de clave privada juega un papel central en el soporte del procesador i.MX 8X para el cifrado y descifrado sobre la marcha. En este caso, el procesador de seguridad utiliza sus recursos para proporcionar las claves privadas que necesita el módulo del motor de encriptación/desencriptación en línea (IEE) del dispositivo, ya que lee o escribe de forma segura en el almacenamiento encriptado, sin la participación del procesador, el controlador DMA o el dispositivo de E/S solicitante.

Basándose en la tecnología TrustZone de Arm integrada en los procesadores Cortex-A35 del dispositivo, el subsistema SECO también trabaja con el SCU durante el proceso de arranque seguro. En este proceso, la SCU interpreta los ajustes de arranque, configura las fuentes de arranque y carga las imágenes de arranque en la memoria interna o externa. A su vez, el subsistema SECO utiliza sus funciones de criptografía para autentificar las imágenes firmadas del firmware después de que se cargan, pero antes de que se ejecuten.

Salvaguardar las pantallas críticas y la funcionalidad de control

Si bien la capacidad de procesar diversas cargas de trabajo de manera eficiente y segura es importante, para las aplicaciones de misión crítica, como las de los segmentos automovilístico e industrial, la capacidad de salvaguardar las capacidades clave es igualmente vital. La familia i.MX 8X de NXP combina sus capacidades de procesamiento con las capacidades certificables de seguridad necesarias para cumplir estos requisitos críticos.

El soporte de seguridad de la familia de procesadores está incorporado en varios niveles, empezando por la fabricación en una tecnología de proceso de silicio sobre aislante (FD-SOI) totalmente agotada que mejora la fiabilidad del sistema. Debido a que la seguridad del sistema depende de una sólida base de seguridad, la combinación de AP habilitados para TrustZone, el subsistema SECO y las capacidades de arranque seguro pueden proporcionar el tipo de entorno de confianza necesario para frustrar las amenazas a la seguridad.

Al mismo tiempo, la capacidad de manejar de forma independiente las tareas de tiempo crítico con el complejo CM4 del usuario y de descargar las tareas críticas del sistema a los subsistemas SCU y SECO ayuda a asegurar que las capacidades de aplicación de misión crítica permanezcan disponibles a pesar de la carga de procesamiento variable. De hecho, NXP extiende este concepto al soporte de pantallas de misión crítica a través de la tecnología SafeAssure de la compañía, que integra una ruta de conmutación por error de la pantalla de hardware preparada para el nivel de integridad de seguridad automotriz B (ASIL B) en los dispositivos i.MX 8X. Con SafeAssure, los usuarios reciben automáticamente una imagen de conmutación por error si el dispositivo detecta un error de integridad de datos o de la GPU. Al ejecutarse en segundo plano, esta imagen de conmutación por error asegura que la información crítica permanezca disponible incluso durante el fallo de la pantalla primaria.

El apoyo a las aplicaciones de seguridad se extiende al acceso a la memoria en los sistemas basados en i.MX 8X. Entre sus interfaces de memoria soportadas, los dispositivos i.MX 8X proporcionan ECC de 8 bits para la memoria de bajo voltaje de doble velocidad de datos 3 (DDR3L). Junto con el ECC en la caché de L2 (véase de nuevo la figura 2), esta capacidad de ECC DDR3L apoya el nivel 3 de integridad de seguridad industrial (SIL 3). La arquitectura i.MX 8X también extiende el soporte ECC a los dispositivos de almacenamiento flash externos. Aquí, un módulo integrado de codificación y decodificación Bose, Ray-Chaudhuri, Hocquenghem (BCH) proporciona un ECC de 62 bits capaz de corregir de 2 a 20 errores de un solo bit dentro de un bloque de datos leídos de estos dispositivos de almacenamiento.

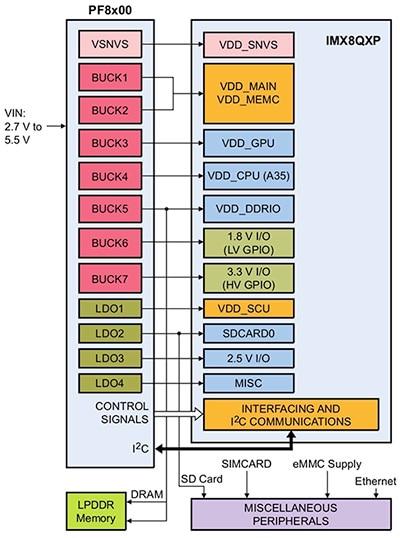

Traer las aplicaciones basadas en i.MX 8X

Como con cualquier procesador de esta clase, la implementación de un diseño basado en i.MX 8X requiere una cuidadosa atención a los estrictos requisitos de potencia, incluyendo las secuencias críticas de encendido. La alimentación de los dispositivos i.MX 8X requiere subir la energía en secuencia o simultáneamente a cuatro grupos de suministro diferentes, comenzando con el subsistema SVNS y continuando con la SCU, las E/S y las interfaces de memoria, y finalmente el resto del dispositivo. Los desarrolladores pueden cumplir este requisito simplemente utilizando los dispositivos de circuito integrado de gestión de energía (PMIC) PF8x00 de NXP, que proporcionan un conjunto completo de rieles de tensión y señales de control necesarias para soportar los procesadores i.MX 8X, así como la memoria externa y los periféricos típicos del sistema (Figura 5).

Figura 5: Los PMIC PF8x00 de NXP proveen un conjunto completo de rieles de voltaje y señales de control necesarias para alimentar los procesadores i.MX 8X. (Fuente de la imagen: NXP Semiconductors)

Figura 5: Los PMIC PF8x00 de NXP proveen un conjunto completo de rieles de voltaje y señales de control necesarias para alimentar los procesadores i.MX 8X. (Fuente de la imagen: NXP Semiconductors)

Al implementar sus propios diseños basados en i.MX 8X, los desarrolladores pueden utilizar el PMICMC33PF8100CCES de NXP que está preprogramado para su uso con procesadores 8QuadXPlus como el MIMX8QX6AVLFZAC. Otras variantes del PF8x00 como el MC33PF8100A0ES y MC33PF8200A0ES soportan los procesadores i.MX 8X, pero no están preprogramados.

Para aplicaciones de seguridad, los dispositivos de la serie PF8200, como el MC33PF8200A0ES, integran características diseñadas para soportar los sistemas ASIL B. Junto con los múltiples monitores internos que incluyen un monitor de voltaje de salida con una referencia de brecha de banda dedicada, los PMIC PF8200 incluyen una clavija de salida a prueba de fallos (FSOB) diseñada para mantener el sistema en un estado seguro durante el encendido o durante un evento de fallo de energía. Además, una rutina de autocomprobación integrada analógica (ABIST) comprueba todos los monitores de voltaje mientras que una rutina de autocomprobación verifica la funcionalidad de otros dispositivos.

Aunque los PMIC PF8x00 pueden simplificar el diseño del hardware de los sistemas basados en i.MX 8X, algunos desarrolladores pueden necesitar comenzar inmediatamente a evaluar los dispositivos i.MX 8X y hacer rápidamente un prototipo de las aplicaciones basadas en i.MX 8X. El kit de habilitación multisensorial (MEK) i.MX 8X deMCIMX8QXP-CPU de NXP proporciona una plataforma de desarrollo lista que combina un procesador i.MX 8QuadXPlus de NXP, un PMIC NXP F8100, 3 gigabytes (Gbyte) de RAM, 32 Gbytes de memoria del controlador multimedia integrado (eMMC) y 64 megabytes (Mbyte) de memoria flash. Junto con la pantalla, la cámara y las interfaces de audio, la placa MEK incluye un conjunto de sensores que se utilizan normalmente en aplicaciones automovilísticas o industriales. Para opciones adicionales de conectividad, audio y expansión, los desarrolladores también pueden agregar la placa base opcional de MCIMX8-8X-BB de NXP.

Conclusión:

Para un número creciente de aplicaciones como la automoción, la industria, el control de edificios y las HMI, las cargas de trabajo de procesamiento se han ampliado para incluir tanto el tradicional procesamiento de E/S en tiempo real como el emergente procesamiento a nivel de aplicación con gráficos multimedia. Aunque existen opciones de diseño para cada tipo de carga de trabajo, son pocas las soluciones disponibles que satisfacen la creciente necesidad de soluciones de alto rendimiento y eficiencia energética capaces de satisfacer los requisitos de los diseños de seguridad certificables en aplicaciones automovilísticas e industriales.

Como se muestra, utilizando una familia de procesadores multinúcleo de NXP Semiconductors, los desarrolladores pueden implementar más eficazmente diseños capaces de satisfacer estos diversos requisitos y escalar fácilmente para abordar los requisitos emergentes de alto rendimiento.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.