Cómo diseñar y certificar sistemas basados en RTD funcionalmente seguros

Colaboración de Editores de DigiKey de América del Norte

2023-07-24

Un detector de temperatura de resistencia (RTD), formado por un transductor y su circuito de acondicionamiento de señales front-end analógico (AFE), es ampliamente utilizado, preciso y fiable. Sin embargo, para aplicaciones de misión crítica y alta fiabilidad, a menudo es necesario diseñar y garantizar un sistema funcionalmente seguro mediante el proceso de certificación de componentes Route 1S o Route 2S.

La certificación de la seguridad funcional de un sistema es un proceso complejo, ya que todos los componentes del sistema deben ser revisados para detectar posibles modos y mecanismos de fallo. Existen varios métodos para diagnosticar fallos y el uso de piezas, que ya están certificadas, alivia esta carga de trabajo junto con el proceso de certificación.

Tenga en cuenta que la "fiabilidad" está relacionada con la seguridad funcional, pero no es lo mismo. En sus términos más sencillos, fiable se refiere a un diseño y una implementación que funcionan según las especificaciones sin problemas ni fallos, mientras que "funcionalmente seguro" significa que cualquier fallo debe ser detectado por el diseño. Tanto la fiabilidad como la seguridad funcional son necesarias para las aplicaciones críticas.

En este artículo se examinan los fundamentos de las RTD y sus circuitos de acondicionamiento de señales en el contexto de la certificación de la seguridad funcional. A continuación, se analizarán los distintos niveles de fiabilidad y certificación de fallos, y lo que se necesita para cumplirlos por ambas vías. Se utilizarán dos CI RTD AFE multicanal, el par AD7124 de Analog Devices, junto con una disposición de placa a placa de evaluación asociada, para ilustrar los puntos clave.

El papel de la seguridad funcional

El papel de la seguridad funcional es proporcionar libertad frente al riesgo inaceptable de lesiones o daños para la salud de las personas mediante la correcta aplicación de una o más funciones automáticas de protección/seguridad. Garantiza que el producto, dispositivo o sistema siga funcionando de forma segura en caso de avería. Es necesario en un amplio abanico de aplicaciones industriales, comerciales e incluso algunas de consumo, como:

- Vehículos autónomos

- Seguridad de las máquinas y robótica

- Sistemas de control industrial (CI)

- Productos domésticos inteligentes

- Fábricas y cadenas de suministro inteligentes

- Sistemas instrumentados de seguridad y sistemas de control de zonas peligrosas

Por ejemplo, en un diseño funcionalmente seguro, la función de un interruptor maestro de encendido/apagado seguiría soportando el apagado, aunque fallaran otros componentes del sistema (Figura 1).

Figura 1: En un sistema funcionalmente seguro, no puede haber duda ni ambigüedad de que este interruptor hará lo que dice que está diseñado para hacer. (Imagen: Pilla vía City Electric Supply Co.)

Figura 1: En un sistema funcionalmente seguro, no puede haber duda ni ambigüedad de que este interruptor hará lo que dice que está diseñado para hacer. (Imagen: Pilla vía City Electric Supply Co.)

Fundamentos de la RTD

¿Por qué fijarse en la temperatura y la seguridad funcional? Una buena razón es que la temperatura es el parámetro físico que más se mide. Suele estar relacionado con aplicaciones de seguridad o críticas, y se apoya en una amplia selección de transductores. Entre ellos están los RTD, que son conceptualmente simples: aprovechan el conocido y repetible Coeficiente de temperatura de resistencia (TCR) de metales como el níquel, el cobre y el platino. Los RTD de platino con resistencia de 100 ohm (Ω) y 1000 Ω a 0 °C son los más utilizados y pueden emplearse en un rango de -200 °C a +850 °C.

Estas RTD tienen una relación resistencia-temperatura muy lineal en este intervalo de temperatura; para situaciones de precisión ultraelevada, existen tablas y factores de corrección y compensación que pueden aplicarse. El RTD de platino con una resistencia nominal de 100 Ω (designado como PT100) tiene una resistencia típica de 18 Ω a -200 °C y 390,4 Ω a +850 °C.

El uso de un RTD requiere que sea excitado por una corriente conocida que suele mantenerse en torno a 1 miliamperio (mA) para minimizar el autocalentamiento. También se utilizan otros valores de corriente, en función de la resistencia nominal de la RTD.

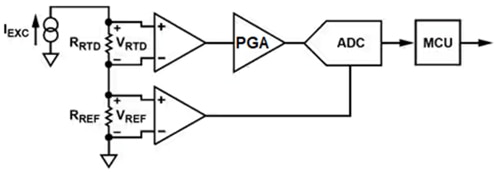

La caída de voltaje a través del RTD se mide simultáneamente mediante un AFE compuesto por un amplificador de ganancia programable (PGA) y, en casi todos los casos, un convertidor de analógico a digital (ADC) junto con una unidad de microcontrolador (MCU) (Figura 2).

Figura 2: El uso de un RTD para medir la temperatura requiere la conducción de una corriente conocida a través del RTD y la medición de la caída de voltaje a través de él, a continuación, aplicar la Ley de Ohm. (Fuente de la imagen: Digi-Key).

Figura 2: El uso de un RTD para medir la temperatura requiere la conducción de una corriente conocida a través del RTD y la medición de la caída de voltaje a través de él, a continuación, aplicar la Ley de Ohm. (Fuente de la imagen: Digi-Key).

La topología del circuito de este esquema básico es idéntica al uso de una resistencia/resistor de detección para determinar la corriente a través de una carga, pero aquí las variables conocidas y desconocidas se conmutan. Para la detección de corriente, la resistencia es conocida mientras que la corriente es desconocida, por lo que el cálculo es I = V/R. En el caso de los RTD, se conoce la corriente, pero no la resistencia, por lo que el cálculo es R = V/I.

El PGA es necesario para mantener la integridad de la señal y maximizar el rango dinámico, ya que los niveles de tensión a través de la RTD pueden oscilar entre decenas de milivoltios y cientos de milivoltios, dependiendo del tipo de RTD y de la temperatura.

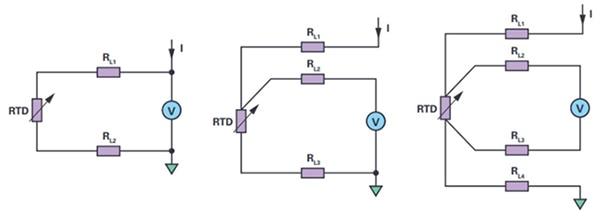

La conexión física entre la fuente de excitación, el RTD y el PGA puede ser una interfaz de dos, tres o cuatro hilos. Aunque en principio basta con dos terminales, hay problemas relacionados con la caída de IR en los terminales de conexión, además de otros artefactos. El uso de las topologías de tres y cuatro hilos en una conexión Kelvin más avanzada da como resultado un rendimiento más preciso y uniforme, aunque aumente los costes de cableado (figura 3).

Figura 3: La RTD puede controlarse y detectarse mediante sólo dos cables (izquierda), pero el uso de tres cables (centro) e incluso cuatro cables (derecha, conexión Kelvin) permite eliminar diversas fuentes de error debidas a los cables. (Fuente de la imagen: Analog Devices).

Figura 3: La RTD puede controlarse y detectarse mediante sólo dos cables (izquierda), pero el uso de tres cables (centro) e incluso cuatro cables (derecha, conexión Kelvin) permite eliminar diversas fuentes de error debidas a los cables. (Fuente de la imagen: Analog Devices).

Empezar por la terminología y las normas

Como ocurre con muchas especialidades, la seguridad funcional tiene muchos términos, conjuntos de datos y acrónimos únicos que se utilizan ampliamente en debates relacionados. Entre ellas están:

- Fallos en el tiempo (FIT): número de fallos que cabe esperar en mil millones (109) de horas de funcionamiento del dispositivo.

- Análisis de los modos de fallo y sus efectos (AMFE): proceso que consiste en examinar el mayor número posible de componentes, conjuntos y subsistemas para identificar los posibles modos de fallo de un sistema, así como sus causas y efectos.

- Análisis de modos de fallo, efectos y diagnóstico (FMEDA): técnica de análisis sistemático para obtener tasas de fallo a nivel de subsistema/producto, modos de fallo y capacidad de diagnóstico.

Los datos FIT son necesarios junto con los análisis de modos de fallo, efectos y diagnóstico (FMEDA) de los distintos componentes del sistema para realizar un análisis completo. FMEA solo ofrece información cualitativa, mientras que FMEDA ofrece información cualitativa y cuantitativa, lo que permite a los usuarios medir un nivel de criticidad de los modos de fallo y ordenarlos según su importancia. FMEDA añade información sobre riesgos, modos de fallo, análisis de efectos y diagnósticos, y fiabilidad.

- Nivel de integridad de la seguridad (SIL): hay cuatro niveles de integridad discretos asociados a SIL: SIL 1, SIL 2, SIL 3 y SIL 4. Cuanto mayor sea el nivel SIL, mayor será el nivel de seguridad asociado y menor la probabilidad de que un sistema no funcione correctamente.

Una clasificación SIL 2 indica que más del 90% de los fallos del sistema pueden diagnosticarse. Para certificar un diseño, el diseñador del sistema debe aportar pruebas a la casa certificadora sobre los fallos potenciales, si son fallos seguros o fallos peligrosos y cómo pueden diagnosticarse.

- La norma IEC 61508, cuyo título oficial es "Seguridad funcional de los sistemas eléctricos, electrónicos y electrónicos programables relacionados con la seguridad" (e informalmente denominada simplemente "Seguridad funcional electrónica"), es la especificación para diseños funcionalmente seguros. Documenta el flujo de diseño necesario para desarrollar una pieza con certificación SIL. Es necesario generar documentación para cada paso, desde el concepto y la definición hasta el diseño, la disposición, la fabricación, el montaje y la prueba.

Este proceso se conoce como Route 1S y es complicado. Sin embargo, existe una alternativa a la Route 1S denominada flujo de la Ruta 2S. Se trata de una ruta "probada en uso" y es aplicable cuando se han diseñado grandes volúmenes del producto en productos y sistemas finales y se están utilizando sobre el terreno con miles de horas de funcionamiento acumuladas.

En el marco del flujo de la Route 2S, un producto aún puede certificarse aportando pruebas a la autoridad de certificación de:

- Volúmenes utilizados sobre el terreno

- Análisis de todas las devoluciones del campo y detalle de que las devoluciones no se debieron a fallos dentro del propio componente.

- Hoja de datos de seguridad en la que se detallan los diagnósticos y la cobertura que ofrecen

- Molde/clavija FMEDA

Fusión de interfaces RTD con el flujo SIL Route 2S

Certificar un sistema es un proceso largo, ya que hay que revisar todos los componentes del sistema para detectar posibles mecanismos de fallo, y existen varios métodos para diagnosticar fallos. El uso de piezas ya certificadas reduce el esfuerzo necesario y acorta el proceso de certificación.

Un componente de interfaz RTD maduro y altamente integrado es clave para facilitar la certificación Route 2S, ya que define un paquete de soluciones completo y, por tanto, puede caracterizarse completamente con datos asociados al uso sobre el terreno y a los fallos. A diferencia de lo que ocurre con el uso de múltiples CI de bloques de construcción más pequeños, en los que deben analizarse sus diversas interfaces e interacciones para la configuración de interconexión específica que se utilice.

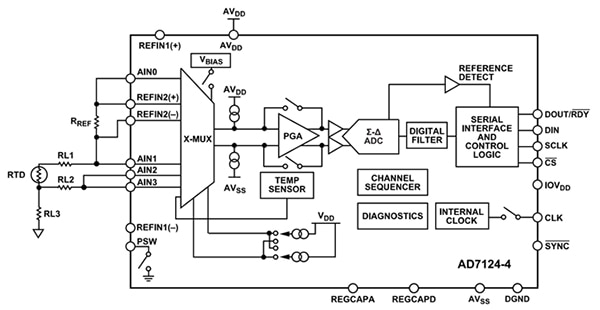

Un ejemplo de ello es el AD7124-4 de cuatro canales (Figura 4) y el AD7124-8 similar de ocho canales (en adelante denominados colectivamente "AD7124" al hablar de las muchas características que tienen en común). Estos componentes son idóneos para el flujo Route 2S debido a sus características de autodiagnóstico y diagnóstico integradas, así como a su "historial" sobre el terreno.

Figura 4: El AD7124-4 de cuatro canales es una cadena de señal sensor-procesador RTD funcionalmente completa. (Fuente de la imagen: Analog Devices).

Figura 4: El AD7124-4 de cuatro canales es una cadena de señal sensor-procesador RTD funcionalmente completa. (Fuente de la imagen: Analog Devices).

Estos CI son soluciones completas para la medición multicanal de RTD e incluyen todos los bloques de construcción necesarios desde un sensor hasta una salida digitalizada y para la comunicación con un microcontrolador asociado. Incluyen el multiplexor multicanal, PGA, ADC sigma-delta de 24 bits, fuentes de corriente para las RTD, referencias de tensión para el funcionamiento interno, reloj del sistema, filtrado analógico y digital e interfaces serie de tres o cuatro hilos para interconexiones compatibles con SPI, QSPI, MICROWIRE y DSP.

Sin embargo, la presencia de estas funciones no proporciona intrínsecamente una base para la cualificación SIL Ruta 2S. Para un diseño funcionalmente seguro, se requiere una matriz de diagnósticos integrados para las numerosas funciones que componen el sistema RTD. Los múltiples diagnósticos integrados en el AD7124 minimizan tanto la complejidad como el tiempo de diseño, y eliminan la necesidad de duplicar la cadena de señales para la cobertura de diagnóstico.

Estos diagnósticos incluyen, entre otros, la supervisión de la fuente de alimentación, la tensión de referencia y la entrada analógica; la detección de un cableado abierto a las RTD; la comprobación del rendimiento de la conversión y la calibración; la comprobación de la funcionalidad de la cadena de señales; la supervisión de las funciones de lectura/escritura; y la supervisión del contenido del registro.

¿Cómo se traducen estas afirmaciones de "alto nivel" en los necesarios diagnósticos en chip? La respuesta tiene muchas facetas:

Diagnóstico SPI: Para cada escritura en el AD7124, el procesador genera un valor de comprobación de redundancia cíclica (CRC) que se anexa a la información que se envía al ADC. A continuación, el ADC genera su propio valor CRC a partir de la información recibida y lo compara con el valor CRC recibido del procesador. Si ambos valores coinciden, la información está intacta y se escribirá en el registro en chip correspondiente.

Si los valores no coinciden, significa que se ha producido un bit de corrupción en la transmisión, y el CI establece una bandera de error que indica que se ha producido una corrupción de datos. El AD7124 también se autoprotege al no escribir la información corrupta en un registro.

Se utiliza un procedimiento CRC similar cuando se lee información del AD7124 al procesador del sistema. Por último, la interfaz también cuenta los pulsos de reloj para asegurarse de que sólo hay ocho pulsos de este tipo con cada trama de datos de lectura o escritura, garantizando así que no se ha producido un fallo de reloj.

Comprobaciones de memoria: También se utiliza un CRC para validar el contenido de los registros al encender o cada vez que se alteran los registros en chip (como al cambiar la ganancia). El proceso CRC también se ejecuta periódicamente para garantizar que ningún bit de memoria se ha "volteado" debido al ruido u otras causas. Si se produce un cambio y posteriormente se indica al procesador que la configuración de los registros se ha dañado, puede reiniciar el ADC y volver a cargar los registros.

Comprobación de la cadena de señales: Todos los voltajes estáticos críticos pueden comprobarse a través del ADC, incluidos los carriles de la fuente de alimentación, las salidas del regulador de baja caída (LDO) y los voltajes de referencia; también puede comprobarse la presencia o ausencia del condensador externo a través del LDO. Además, se puede aplicar un voltaje conocido a la entrada del ADC para comprobar el ADC y los ajustes de la función de ganancia. Además, se pueden inyectar corrientes conocidas a través de las entradas analógicas para comprobar si hay una RTD abierta o en cortocircuito.

Conversión y calibración: Los resultados de la conversión ADC se comprueban continuamente para ver si van a todos los ceros o a la escala completa, cualquiera de los cuales indica un problema. El flujo de bits del modulador en el núcleo del ADC se supervisa para garantizar que no se ha saturado y, si se produce la saturación (es decir, si se han producido 20 unos o ceros consecutivos en el modulador), se activa un indicador de error.

Frecuencia del reloj maestro: La frecuencia de este reloj no sólo controla las tasas de conversión, sino que también establece las frecuencias de entalla de los filtros digitales de 50/60 Hertz (Hz). Un registro interno del AD7124 permite al procesador complementario cronometrar y, por tanto, comprobar la precisión del reloj maestro.

Características adicionales: El AD7124 incluye un sensor de temperatura, que también se puede utilizar para controlar la temperatura del molde. Ambas versiones tienen una clasificación de descarga electrostática (Descarga electrostática) de 4 kilovoltios (kV) para un rendimiento robusto, y ambas están alojadas en un receptáculo LFCSP de 5 × 5 milímetros (mm) adecuado para diseños intrínsecamente seguros.

Debido a la complejidad interna, la sofisticación y las funciones avanzadas de autocomprobación de los AD7124-4 y AD7124-8, tiene sentido disponer de un medio para ejercitar y evaluar los CI.

Para ello, Analog Devices ofrece un par de placas conectadas: la placa de evaluación EVAL-AD7124-4SDZ para el AD7124-4 (Figura 5) y la placa de interfaz/plataforma de demostración del sistema EVAL-SDP-CB1Z SDP(Figura 6). El primero es específico del AD7124-4 y funciona conjuntamente con el segundo, que proporciona comunicación con el PC del usuario y el software de evaluación a través de un enlace USB.

Figura 5: La EVAL-AD7124-4SDZ es una placa de evaluación para el AD7124-4. (Fuente de la imagen: Analog Devices).

Figura 5: La EVAL-AD7124-4SDZ es una placa de evaluación para el AD7124-4. (Fuente de la imagen: Analog Devices).

Figura 6: La placa de interfaz EVAL-SDP-CB1Z es un complemento de la placa de evaluación EVAL-AD7124-4SDZ que proporciona una conexión USB a un PC. (Fuente de la imagen: Analog Devices).

Figura 6: La placa de interfaz EVAL-SDP-CB1Z es un complemento de la placa de evaluación EVAL-AD7124-4SDZ que proporciona una conexión USB a un PC. (Fuente de la imagen: Analog Devices).

La disposición de evaluación se apoya en el software AD7124-4 EVAL+, que configura completamente la funcionalidad del registro del dispositivo AD7124-4 y ejercita el CI. También proporciona análisis en el dominio del tiempo en forma de gráficos de forma de onda, histogramas y análisis de ruido asociado para la evaluación del rendimiento del ADC.

Transición a un diseño funcionalmente seguro

Es importante tener en cuenta que los modelos AD7124-4 y AD7124-8 no tienen clasificación SIL, lo que significa que no han sido diseñados y desarrollados siguiendo las directrices de desarrollo definidas por la norma IEC 61508. Sin embargo, si se comprende la aplicación final y se utilizan adecuadamente los distintos diagnósticos, puede evaluarse su uso en un diseño SIL.

El camino hacia la certificación Route 1S tiene múltiples consideraciones para analizar y abordar los fallos, que pueden ser sistémicos o aleatorios. Los fallos sistémicos se deben a defectos de diseño o fabricación, como una interrupción ruidosa por falta de filtrado en el pin/clavija de interrupción externo o un margen de sobrecarga insuficiente para una señal. En cambio, los fallos aleatorios se deben a causas físicas como la corrosión, el estrés térmico o el desgaste.

Una preocupación importante es el llamado fallo peligroso no detectado, que se aborda mediante múltiples técnicas. Para minimizar los fallos aleatorios, los diseñadores utilizan una o las tres tácticas:

- Componentes más fiables y menos estresados.

- Diagnósticos que se basan en mecanismos de detección integrados implementados mediante hardware o software.

- Tolerancia a fallos mediante circuitos redundantes. Si se añade una ruta redundante, se puede tolerar un solo fallo. Esto se denomina sistema de tolerancia a fallos de hardware 1 (HFT 1), lo que significa que un fallo no puede provocar el fallo del sistema.

Una herramienta para comprender la cobertura del nivel SIL es una matriz que traza la fracción de fallo seguro (SFF) (la cantidad de cobertura de diagnóstico) y la tolerancia a fallos del hardware (la redundancia) (Figura 7).

|

|||||||||||||||||||||||

Figura 7: Esta matriz caracteriza la fracción de fallo seguro (SFF) frente a la tolerancia a fallos del hardware (HFT) y ofrece una visión de la cobertura SIL. (Fuente de la imagen: Analog Devices)

Las filas muestran la cantidad de cobertura de diagnóstico, mientras que las columnas muestran la tolerancia a fallos del hardware. Un HFT de 0 significa que si se produce un fallo en el sistema, se perderá la función de seguridad. Un mayor nivel de diagnóstico reduce la cantidad necesaria de redundancia del sistema o mejora el nivel SIL de la solución con el mismo nivel de redundancia (descendiendo en la matriz).

Tenga en cuenta que la FMEDA de una aplicación de temperatura típica que utiliza estos dispositivos muestra una fracción de fallo seguro (SFF) superior al 90% según la norma IEC 61508. Normalmente se necesitarían dos ADC tradicionales para proporcionar este nivel de cobertura a través de la redundancia, pero el AD4172 solo requiere un único ADC, lo que proporciona un ahorro significativo en el coste de la lista de materiales (BOM) y en el espacio de la placa.

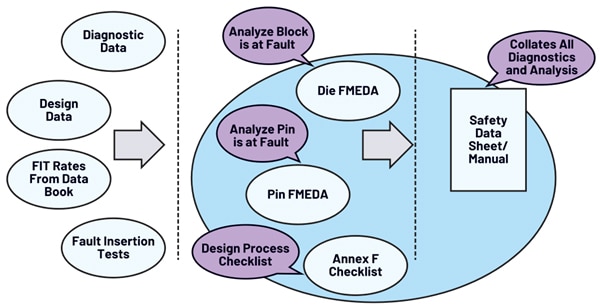

Documentación para diseños SIL

Para obtener la certificación Route 1S se necesita una amplia documentación. Entre los documentos fuente necesarios se encuentran:

- Hoja de datos de seguridad (el manual de seguridad de una pieza con clasificación SIL)

- FMEDA de pin y FMEDA de molde, con modos de fallo, efectos y análisis para ambos.

- Lista de comprobación del anexo F (definido por la norma IEC 61508)

Esta documentación, a su vez, procede de diversas fuentes (Figura 8):

- Los datos de diagnóstico de la hoja de datos recogen todas las características de diagnóstico disponibles en la pieza.

- Los datos de diseño se refieren a datos internos. Por ejemplo, el área del Molde y el Impacto de cada bloque interno de la pieza.

- FIT, con índices para varios componentes, están disponibles en el libro de datos.

- Las pruebas de inserción de fallos se realizan para bloques que no pueden analizarse utilizando datos de diseño y diagnóstico. Estas pruebas se planifican en función de los requisitos de la aplicación, y el resultado de las pruebas de inserción de fallos se utiliza para reforzar los documentos FMEDA y FMEA.

Figura 8: Las diversas fuentes de documentación se agregan y extraen para proporcionar el paquete de información completo necesario para la certificación SIL. (Fuente de la imagen: Analog Devices).

Figura 8: Las diversas fuentes de documentación se agregan y extraen para proporcionar el paquete de información completo necesario para la certificación SIL. (Fuente de la imagen: Analog Devices).

Más detalles sobre las especificaciones:

- En el Manual de seguridad u Hoja de datos de seguridad se utiliza toda la información recopilada para proporcionar los requisitos necesarios que permitan la integración del AD7124-4 o AD7124-8. Recopila todos los diagnósticos y análisis procedentes de diversos documentos y conjuntos de datos.

- El Molde FMEDA para el AD7124-4 y el AD7124-8 analiza los bloques principales del esquema de aplicación, identifica los modos y efectos de los fallos y comprueba el diagnóstico y los análisis para una función de seguridad concreta. Por ejemplo, el análisis del módulo de reloj muestra los modos de fallo, el efecto de cada uno en la salida, la cantidad de cobertura de diagnóstico y un análisis del impacto (Figura 9).

|

Figura 9: Esta tabla define el modo de fallo, los efectos, el diagnóstico y el análisis del bloque de reloj maestro. (Fuente de la imagen: Analog Devices)

El resultado de este Molde FMEDA es una presentación cuantitativa de los índices de fallos seguros, fallos peligrosos detectados y fallos peligrosos no detectados. Todo ello se utiliza para calcular el SFF.

El pin FDEMA contempla los fallos desde una perspectiva diferente. Analiza varios tipos de fallos en las clavijas del AD7124-4 y AD7124-8 y su resultado para la aplicación RTD. Hace esto para cada pin individual y describe el resultado para el caso en que el pin se abra, cortocircuite con la alimentación/tierra o cortocircuite con pines adyacentes.

La lista de comprobación del anexo F es una lista de comprobación de medidas de diseño para evitar fallos sistemáticos. Comprende:

- Descripción general del producto

- Información sobre las aplicaciones

- Concepto de seguridad

- Previsiones de por vida

- FIT

- Cálculos FMEDA-SFF y CC

- Mecanismos de seguridad del hardware

- Descripción del diagnóstico

- Solidez CEM

- Funcionamiento en configuraciones redundantes

- Anexos y lista de documentos

En resumen, la certificación de la seguridad funcional de un componente recién introducido a través de la Route 1S es larga, compleja, lenta, intensa y exhaustiva. Afortunadamente, la Route 2S, como ya se ha mencionado, es un enfoque alternativo viable para algunos componentes.

Route 2S: Una ruta alternativa

La ruta conocida como Route 2S es aplicable para una pieza liberada con experiencia y datos de campo y se designa como "probada en uso". Se basa en un análisis de las devoluciones de clientes y el número de aparatos enviados. No puede utilizarse con piezas nuevas que tengan poco o ningún "historial" de exposición en uso real.

La Route 2S permite la certificación SIL como si la pieza se hubiera analizado completamente según la norma IEC 61508. Está a disposición de los diseñadores de módulos y sistemas si han utilizado con éxito el CI en cuestión en el pasado y conocen la tasa de fallos sobre el terreno. Las características de prueba y verificación integradas, junto con los datos de rendimiento, convierten a los modelos AD7214-4 y AD7214-8 en buenos candidatos para Route 2S.

Recurrir a la ROute 2S requiere datos detallados y estadísticamente significativos sobre devoluciones y fallos en el campo. Este requisito es mucho más difícil de cumplir para los proveedores de CI que para los de placas o módulos. La razón es que, por lo general, los primeros no tienen suficiente conocimiento de la aplicación final, ni de qué porcentaje de las unidades defectuosas procedentes del campo les son devueltas para su análisis.

Conclusión:

La Route 1S para la certificación funcionalmente segura de nuevos productos es exhaustiva y detallada. También es un reto técnico y, sin duda, requiere mucho tiempo. En cambio, el proceso Route 2S permite certificar los productos liberados basándose en la experiencia sobre el terreno, los fallos y los datos de análisis. Esta es una ruta útil que es soportada por los CI de interfaz RTD AD7214-4 y AD7214-8 ya que tienen el historial requerido. Igualmente importante es el hecho de que estos CI incorporan numerosas funciones y características de diagnóstico y autodiagnóstico que los convierten en candidatos idóneos para dicha certificación.

Contenido relacionado

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.