Por qué y cómo usar las FPGA de Efinix para imágenes AI/ML - Parte 1: Primeros pasos

Colaboración de Editores europeos de DigiKey

2023-04-20

Nota del editor: Los nuevos enfoques de las arquitecturas FPGA aportan un control más preciso y una mayor flexibilidad para responder a las necesidades del aprendizaje automático (ML) y la inteligencia artificial (AI). La primera parte de esta serie en dos partes presenta una de estas arquitecturas de Efinix y cómo empezar a utilizarla con una placa de desarrollo. En la Parte 2 se analiza la interconexión de la placa de desarrollo con dispositivos y periféricos externos, como una cámara.

Las FPGA desempeñan un papel fundamental en muchas aplicaciones, desde el control industrial y la seguridad hasta la robótica, la industria aeroespacial y la automoción. Gracias a la naturaleza flexible del núcleo lógico programable y a sus amplias capacidades de interconexión, un caso de uso cada vez más frecuente de las FPGA es el procesamiento de imágenes cuando se va a desplegar la inferencia ML. Las FPGA son ideales para implementar soluciones que tengan varias interfaces de cámara de alta velocidad. Además, las FPGA también permiten implementar canalizaciones de procesamiento dedicadas en la lógica, con lo que se eliminan cuellos de botella que estarían asociados a soluciones basadas en CPU o GPU.

Para muchos desarrolladores, sin embargo, sus aplicaciones requieren más funcionalidad ML/AI y un control o enrutamiento y lógica más precisos, más allá de lo que pueden ofrecer las arquitecturas FPGA clásicas con bloques lógicos combinatorios (CLB). Los enfoques más recientes de las arquitecturas FPGA abordan estos problemas. Por ejemplo, la arquitectura Quantum de Efinix utiliza un bloque de lógica y enrutamiento intercambiables (XLR).

En este artículo se analizan las principales Características y atributos de la arquitectura FPGA de Efinix, se hace hincapié en sus capacidades AI/ML y se presentan implementaciones en el mundo real. A continuación, analiza una placa de desarrollo y las herramientas asociadas que los desarrolladores pueden utilizar para empezar rápidamente con su próximo diseño de imágenes AI/ML.

Dispositivos FPGA de Efinix

Efinix ofrece actualmente dos gamas de dispositivos. Presentó inicialmente la familia Trion, que ofrece densidades lógicas de 4000 (4K) a 120K elementos lógicos (LE) y se fabrica mediante un proceso SMIC 40LL. La nueva línea de dispositivos, la familia Titanium, ofrece densidades lógicas de 35,000 a 1 millón (1M) de elementos lógicos y se fabrica en el popular nodo de 16 nanómetros (nm) de TSMC.

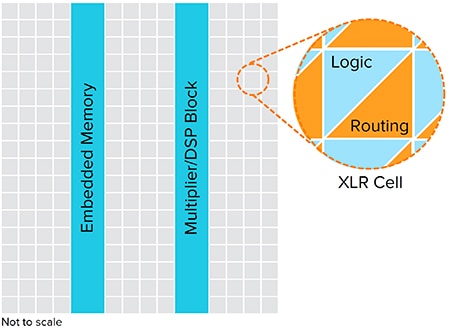

Ambas ofertas se basan en la arquitectura Quantum, única en el mundo de las FPGA. La arquitectura FPGA estándar se basa en CLB que, en el nivel más simple, contienen una tabla de consulta (LUT) y biestables. Los CLB implementan ecuaciones lógicas que luego se interconectan mediante enrutamiento. La arquitectura Quantum de Efinix se aleja de los bloques lógicos y de enrutamiento diferenciados con el bloque XLR.

Lo que hace único a un bloque XLR es que puede configurarse para funcionar como una celda lógica con una LUT, un registro y sumador o una matriz de enrutamiento. Este enfoque ofrece una arquitectura más detallada que proporciona flexibilidad de enrutamiento, lo que permite que las implementaciones que utilizan mucha lógica o mucho enrutamiento alcancen el rendimiento deseado.

Figura 1: Lo que hace único a un bloque XLR es que puede configurarse para funcionar como una celda lógica con una LUT, un registro y sumador o una matriz de enrutamiento. (Fuente de la imagen: Efinix)

Figura 1: Lo que hace único a un bloque XLR es que puede configurarse para funcionar como una celda lógica con una LUT, un registro y sumador o una matriz de enrutamiento. (Fuente de la imagen: Efinix)

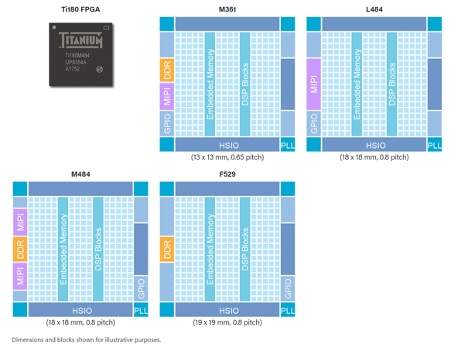

Como familia más reciente, los dispositivos Titanio ofrecen las características más avanzadas para el desarrollador (Figura 2). Junto con el núcleo XLR, proporcionan enlaces serie multigigabit que funcionan a 16 gigabits por segundo (Gbps) o 25.8 Gbps, según el dispositivo seleccionado. Estos enlaces multigigabit son cruciales para permitir la transferencia de datos a alta velocidad dentro y fuera del chip.

Figura 2: Titanium FPGA Ti180 se ofrece en una variedad de opciones según el ancho del bus, E/S y requisitos de memoria. (Fuente de la imagen: Efinix)

Figura 2: Titanium FPGA Ti180 se ofrece en una variedad de opciones según el ancho del bus, E/S y requisitos de memoria. (Fuente de la imagen: Efinix)

Los dispositivos Titanium también ofrecen una amplia gama de capacidades de interconexión de entrada/salida (E/S) que pueden agruparse como E/S de uso general (GPIO) y que admiten estándares de E/S de un solo extremo, como CMOS de bajo voltaje (LVCMOS) a 3.3 voltios, 2.5 voltios y 1.8 voltios.

Para la interconexión diferencial y de alta velocidad, los dispositivos Titanium proporcionan E/S de alta velocidad (HSIO) que admite estándares de E/S de un solo extremo como LVCMOS a 1.2 voltios, 1.5 voltios y SSTL y HSTL. Los estándares de E/S diferenciales compatibles con HSIO incluyen la señal diferencial de bajo voltaje (LVDS), SSTL diferencial y HSTL.

Las FPGA modernas también requieren una memoria estrechamente acoplada y de gran ancho de banda, que se utiliza para almacenar fotogramas de imágenes para aplicaciones de procesamiento de imágenes, datos de muestras para procesamiento de señales y, por supuesto, para ejecutar sistemas operativos y software para procesadores implementados dentro de la FPGA. La gama de dispositivos Titanium ofrece la posibilidad de interactuar con la cuarta velocidad de datos dinámica (DDR4) y la DDR4(x) de bajo consumo (LPDDR4(x)). Dependiendo del dispositivo Titanium seleccionado, el ancho de bus soportado es x32 (J) o x16 (M), mientras que algunos dispositivos no soportan LPDDR4 (L).

Las Titanium FPGA se basan en SRAM y requieren una memoria de configuración, con la configuración del dispositivo realizada por Interconexión periférica serial (SPI) maestro/esclavo o JTAG. Para garantizar la seguridad de este método de configuración, la Titanium FPGA utiliza el Estándar de encriptación avanzada (AES GCM) del flujo de bits, junto con AES GCM y RSA-4096 para proporcionar autenticación del flujo de bits. Se requiere una seguridad sólida como esta, ya que las FPGA se despliegan en el borde, donde los actores maliciosos podrían acceder y manipular su comportamiento.

Presentación de la placa de desarrollo

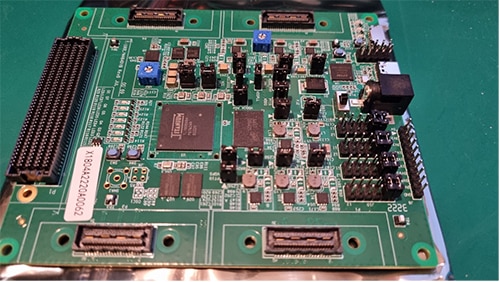

Las placas de desarrollo constituyen un elemento fundamental del proceso de evaluación de FPGA, ya que pueden utilizarse para explorar las capacidades de un dispositivo y crear prototipos de aplicaciones, contribuyendo así a reducir el riesgo global. La primera placa de desarrollo disponible para evaluar las Titanium FPGA y empezar a crear prototipos de aplicaciones es la Ti180 M484 (Figura 3). La placa cuenta con un conector de tarjeta mezzanine FPGA (FMC) y cuatro conectores Samtec QSE.

Figura 3: Junto con una Titanium FPGA, el kit de desarrollo Ti180 M484 incorpora un conector FMC y cuatro conectores Samtec QSE. (Fuente de la imagen: Adam Taylor)

Figura 3: Junto con una Titanium FPGA, el kit de desarrollo Ti180 M484 incorpora un conector FMC y cuatro conectores Samtec QSE. (Fuente de la imagen: Adam Taylor)

La FPGA Ti180 instalado en esta placa de desarrollo proporciona 172,000 celdas XLR, 32 relojes globales, 640 elementos de Procesador de señal digital (DSP) y 13 megabits (Mbits) de RAM integrada. Los elementos del procesador de señal digital (DSP) permiten realizar multiplicaciones de 18 x 19 en coma fija y multiplicaciones de 48 bits. Este procesador de señal digital (DSP) también puede optimizarse para operaciones de instrucción única y datos múltiples (SIMD) funcionando en configuración doble o cuádruple. Los elementos DSP también pueden configurarse para realizar operaciones de punto flotante.

Como la mayoría de las placas de desarrollo, la placa de desarrollo Ti180 dispone de LED y botones sencillos. Sin embargo, su verdadera potencia reside en su capacidad de interconexión. La placa de desarrollo Ti180 proporciona un conector FMC de bajo número de patillas que permite conectar una amplia gama de periféricos. Al tratarse de un estándar ampliamente utilizado, existen muchas tarjetas FMC que permiten la interconexión de convertidores de analógico a digital (ADC) de alta velocidad, convertidores de digital a analógico (DAC), redes y soluciones de memoria/almacenamiento.

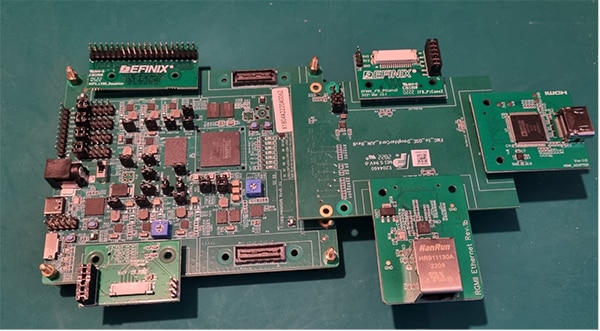

Además de la conexión FMC, la placa proporciona cuatro conectores Samtec QSE que permiten al desarrollador añadir tarjetas de expansión. Estos conectores QSE se utilizan para proporcionar entradas y salidas MIPI, y cada conector QSE proporciona una entrada o una salida MIPI.

Figura 4: Se muestra el kit de desarrollo Ti180 M484 con su versátil gama de opciones de ampliación basadas en conectores QSE y FMC. (Fuente de la imagen: Adam Taylor)

Figura 4: Se muestra el kit de desarrollo Ti180 M484 con su versátil gama de opciones de ampliación basadas en conectores QSE y FMC. (Fuente de la imagen: Adam Taylor)

La placa Ti180 también proporciona 256 Mbits de LPDDR4 para soportar la memoria de alto rendimiento necesaria en aplicaciones de procesamiento de imágenes o señales. Además, la placa de desarrollo ofrece diversas opciones de reloj a 25, 33.33, 50 y 74.25 megahercios (MHz), que pueden utilizarse con el bucle de fase cerrado (PLL) del dispositivo para generar distintas frecuencias internas.

La capacidad de reprogramar y depurar en vivo en la placa durante el desarrollo es fundamental y requiere una conexión JTAG, que se proporciona a bordo a través de una interfaz USB-C. También se proporciona memoria no volátil en forma de dos dispositivos NOR Flash de 256 Mbit que pueden utilizarse para demostrar la solución de configuración.

La placa se alimenta de un adaptador de corriente universal de 12 voltios que se incluye en la caja. También se incluye una salida de FMC a QSE, junto con tarjetas de expansión basadas en QSE para HDMI, Ethernet, MIPI y LVDS. Para demostrar las capacidades de procesamiento de imágenes de Ti180, también se proporciona una tarjeta dependiente RPI dual y dos tarjetas de cámara IMX477.

El entorno informático

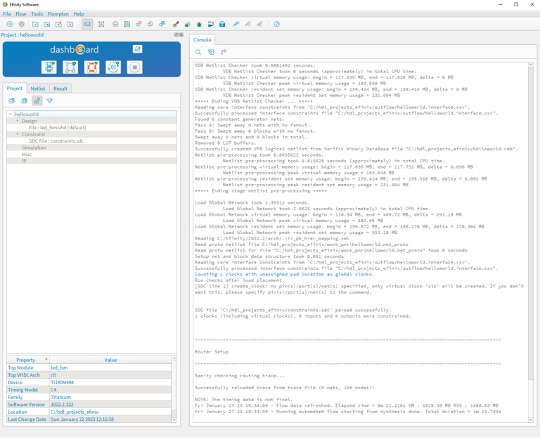

Los diseños de implementación dirigidos a la placa de desarrollo Ti180 utilizan el software Efinity de Efinix. El software permite generar un flujo de bits mediante síntesis y ubicación y enrutamiento. También proporciona a los desarrolladores bloques de propiedad intelectual (IP), análisis de temporización y depuración en chip.

Tenga en cuenta que se necesita una placa de desarrollo para poder acceder al software Efinity. Sin embargo, a diferencia de otros proveedores, la herramienta no tiene versiones diferentes que requieran licencias adicionales.

En Efinity, se crean nuevos proyectos dirigidos al dispositivo seleccionado. A continuación, pueden añadirse archivos Nivel de transferencia de registro al proyecto y crearse restricciones para el diseño de temporización y E/S. Es en Efinity donde los desarrolladores también pueden implementar el diseño de E/S, utilizando HSIO, GPIO y E/S especializadas.

Figura 5: Dentro de Efinity, se crean nuevos proyectos dirigidos al dispositivo seleccionado. (Fuente de la imagen: Adam Taylor)

Figura 5: Dentro de Efinity, se crean nuevos proyectos dirigidos al dispositivo seleccionado. (Fuente de la imagen: Adam Taylor)

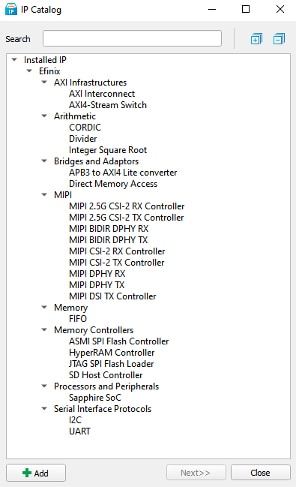

Un elemento fundamental del diseño de FPGA es el aprovechamiento de IP, especialmente en el caso de IP complejas como las interconexiones AXI, los controladores de memoria y los procesadores de núcleo blando. Efinity proporciona a los desarrolladores una serie de bloques IP que pueden utilizarse para acelerar el proceso de diseño.

Figura 6: Efinity proporciona a los desarrolladores un catálogo de IP que pueden utilizar para acelerar el proceso de diseño. (Fuente de la imagen: Adam Taylor)

Figura 6: Efinity proporciona a los desarrolladores un catálogo de IP que pueden utilizar para acelerar el proceso de diseño. (Fuente de la imagen: Adam Taylor)

Aunque las FPGA son excelentes para implementar estructuras de procesamiento paralelo, muchos diseños de FPGA incluyen procesadores de núcleo blando. Permiten realizar procesos secuenciales, como las comunicaciones de red. Para permitir el despliegue de los procesadores softcore en los dispositivos Efinix, Efinity proporciona la herramienta de configuración de sistemas en chip (SoC) Sapphire. Sapphire permite al desarrollador definir un sistema multiprocesador que disponga de cachés y coherencia de caché en varios procesadores, junto con la capacidad de ejecutar un sistema operativo Linux integrado. Dentro de Sapphire, el desarrollador puede elegir entre uno y cuatro procesadores de núcleo blando.

El procesador de núcleo blando que se está implementando es la CPU blanda VexRiscV, que se basa en la arquitectura del conjunto de instrucciones RISC-V. El procesador VexRiscV es una implementación de 32 bits que cuenta con extensiones para pipelining y ofrece un conjunto de características configurables, lo que lo hace ideal para su implementación en dispositivos Efinix. Las configuraciones opcionales incluyen un multiplicador, instrucciones atómicas, extensiones de coma flotante e instrucciones comprimidas. Según la configuración del sistema en chip (SoC), el rendimiento oscilará entre 0,86 y 1,05 DMIPS/MHz.

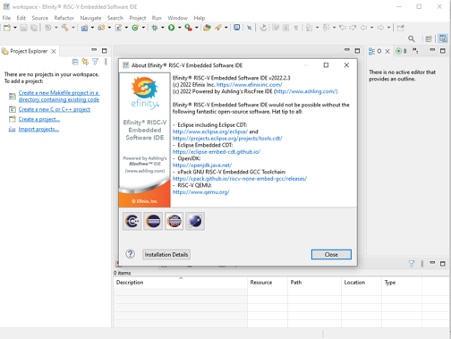

Una vez diseñado e implementado el entorno de hardware en el dispositivo Efinix, el software de aplicación puede desarrollarse utilizando el IDE RiscFree de Ashling. Ashling RiscFree es un entorno completo de desarrollo integrado (IDE) basado en Eclipse que permite crear y compilar software de aplicación, así como depurar en el destino para ajustar la aplicación antes de su despliegue.

Figura 7: Ashling RiscFree es un IDE basado en Eclipse que permite crear y compilar software de aplicación, además de depurarlo en el objetivo. (Fuente de la imagen: Adam Taylor)

Figura 7: Ashling RiscFree es un IDE basado en Eclipse que permite crear y compilar software de aplicación, además de depurarlo en el objetivo. (Fuente de la imagen: Adam Taylor)

Si se está desarrollando una solución Linux embebida, se proporcionan todos los artefactos de arranque necesarios, incluidos First Stage Boot Loader, OpenSBI, U-Boot y Linux mediante Buildroot. Como alternativa, el desarrollador puede utilizar FreeRTOS si necesita una solución en tiempo real.

Aplicación de la IA

Sobre la base de la operación softcore de RISC-V se encuentra la implementación de IA de Efinix. Esto aprovecha la capacidad de instrucción personalizada del procesador RISC-V para permitir la aceleración de las soluciones TensorFlow Lite. El uso del procesador RISC-V también permite a los usuarios crear instrucciones personalizadas que pueden utilizarse como parte del preprocesamiento o postprocesamiento a la inferencia de IA, creando una solución más sensible y determinista.

Para empezar a implementar la IA, el primer paso es explorar el zoo de modelos de Efinix, que es una biblioteca de modelos de IA/ML optimizada para su tecnología final. Los desarrolladores que trabajan con los dispositivos Efinix pueden acceder al zoo del modelo y entrenar la red mediante Jupyter Notebooks o Google Colab. Una vez entrenada la red, puede convertirse de un modelo en coma flotante a otro cuantizado utilizando el conversor TensorFlow Lite.

Una vez en el formato TensorFlow Lite, el acelerador tinyML de Efinix puede utilizarse para crear una solución desplegable en la solución RISC-V. El generador tinyML permite al desarrollador personalizar la implementación del acelerador y generar los archivos del proyecto. Cuando se implanta de esta forma, la aceleración puede oscilar entre 4x y 200x en función de la arquitectura y la personalización seleccionadas.

Conclusión:

Los dispositivos Efinix ofrecen flexibilidad a los desarrolladores gracias a su exclusiva arquitectura XLR. La cadena de herramientas no solo permite realizar diseños RTL, sino también implementar complejas soluciones SoC que utilizan procesadores RISC-V de núcleo blando. Encima del SoC de núcleo blando hay una solución AI/ML que permite el despliegue de la inferencia ML.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.