Diseño en alimentación a través de internet de alta potencia utilizando soluciones IEEE 802.3bt listas para usar

Colaboración de Editores de DigiKey de América del Norte

2019-05-09

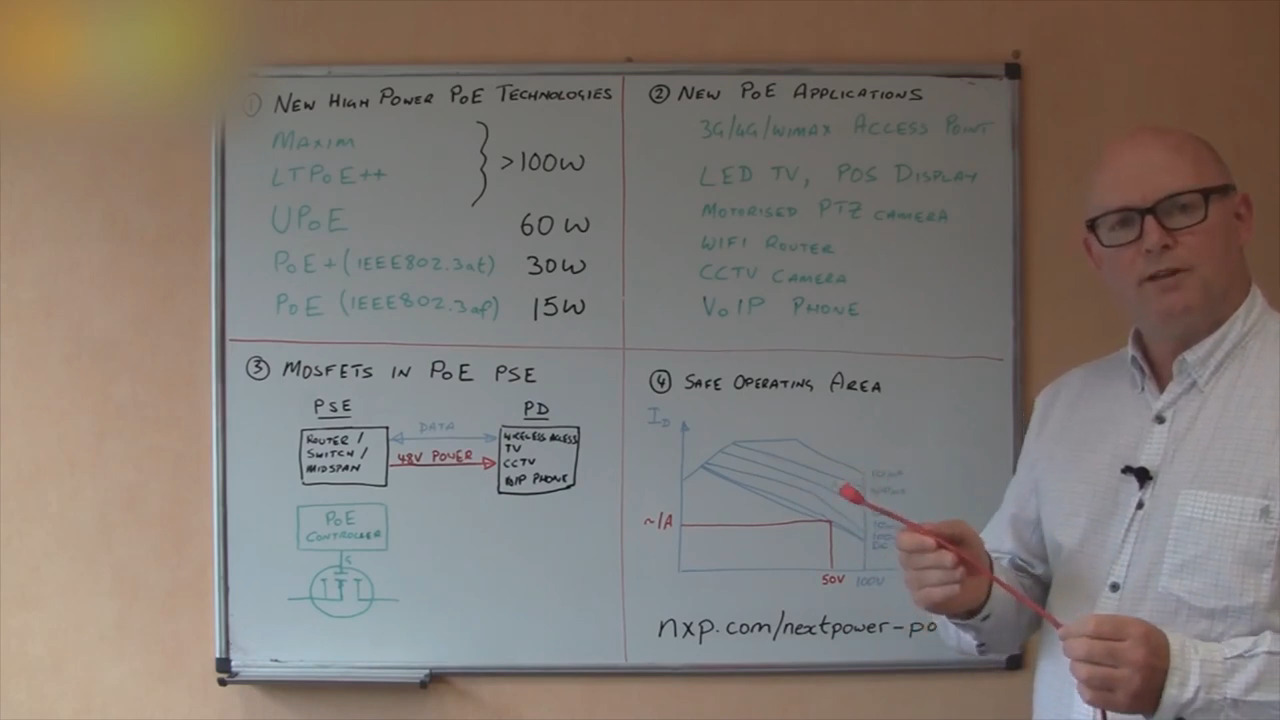

Desde la introducción de la alimentación por Ethernet (PoE) en 2003, su capacidad de entrega de potencia ha aumentado dramáticamente de sus 15.4 vatios originales a 30 vatios, pero los diseñadores aún necesitan más para sus aplicaciones. Una nueva modificación a la especificación de PoE, IEEE 802.3bt, aborda esa necesidad al permitir hasta 60 vatios (y en algunas aplicaciones hasta 90 vatios) en la fuente de alimentación.

La modificación se ratificó a finales de 2018. Los primeros controladores comerciales integrados de Equipo de fuente de alimentación (PSE) y las interfaces del Dispositivo accionado (PD) están ahora disponibles, lo que permite que los ingenieros de diseño aprovechen lo que ahora se llama "PoE de alta potencia".

Este artículo describe cómo IEEE 802.3bt difiere de las versiones anteriores de PoE, antes de introducir los controladores PSE integrados y las interfaces de PD de Microsemi, Texas Instruments (TI), Linear Technology, and Nexperia. Describe cómo aplicar mejor estos dispositivos para construir un sistema, abordando consideraciones importantes como la protección del circuito y los requisitos de diseño y disposición.

¿Qué es IEEE 802.3bt?

El estándar original (IEEE 802.3af) especificó hasta 15.4 vatios en la fuente de alimentación, lo que sobraba para aplicaciones como teléfonos IP y puntos de acceso a Wi-Fi, pero no era lo suficiente para aplicaciones posteriores como teléfonos IP con video o cámaras pan-tilt-zoom (PTZ). La modificación de 2009 a la especificación (IEEE 802.3at) resolvió ese problema especificando 30 vatios en la fuente de alimentación. En los últimos años, ha aumentado la demanda de potencia aún más para admitir aplicaciones conectadas a Ethernet, como terminales de punto de venta (POS), puntos de acceso IEEE 802.11ac e iluminación led en red.

Para abordar la necesidad de más potencia, la nueva modificación IEEE 802.3bt (PoE de alta potencia) a la especificación anterior de PoE y PoE+ aumenta la potencia de salida mínima de PSE y la potencia de entrada mínima de PD. El cambio más importante es que la potencia se puede transmitir a través de los cuatro pares trenzados en un cable Ethernet Cat5e. PoE y PoE+ utilizaron solo dos de los pares trenzados: las líneas de datos en aplicaciones "Alternativa A" o las líneas de repuesto en aplicaciones "Alternativa B". (Consulte el artículo de la biblioteca DigiKey, "Introducción a Alimentación por Ethernet").

La nueva especificación también impulsó la introducción de PSE y PD "Tipo 3" y "Tipo 4" (que pueden soportar 60 vatios y 90 vatios, respectivamente) y Clases adicionales (5-8) para la potencia de salida y entrada (Tabla 1). El diseñador debe tener en cuenta que la modificación está diseñada para cumplir con los requisitos de la fuente de alimentación limitada y voltaje extrabajo de seguridad (SELV) de ISO/IEC 60950 que restringen la potencia a un máximo de 100 vatios por puerto.

|

Tabla 1: Comparación de PoE de alta potencia (IEEE 802.3bt) con PoE (IEEE 802.3af) y PoE+ (IEEE 802.3at). IEEE 802.3bt introduce mayor potencia junto con los nuevos tipos de PSE y PD, así como las nuevas clases. (Fuente de la tabla: Microsemi)

Mejoras producidas por IEEE 802.3bt

Además de la mayor potencia disponible con PoE de alta potencia, la especificación introduce otras funcionalidades. Las mejoras clave incluyen:

- Funcionalidad de clase automática

- Soporte de baja potencia en modo de espera

- Capacidad de potencia extendida si se conoce la longitud del canal (cable)

La clasificación automática (o "Autoclass") es un nuevo mecanismo de clasificación (opcional) exclusivo del PoE de alta potencia que permite que un PD comunique su consumo máximo de energía efectivo al PSE, lo que permite que el PSE establezca el presupuesto de energía para que coincida exactamente con el nivel (más alguna reserva para pérdidas de canal y un margen de "seguridad") para una mejor eficiencia del sistema.

Para alimentar aplicaciones con requisitos de modo de espera estrictos, el PoE de alta potencia incluye un cambio significativo en la duración mínima de la corriente pulsada que se utiliza para garantizar que el PSE mantenga la potencia. Anteriormente, los PD Tipo 1 y 2 usaban una "firma de potencia de mantenimiento" (MPS) que comprende una corriente pulsada de 10 miliamperios (mA) durante al menos 75 milisegundos (ms) cada 325 ms, y una impedancia de CA inferior a 26.3 kiloohms (kΩ) en paralelo con 0.05 microfaradios (μF). El cambio provocado por la especificación IEEE 802.3bt (que se aplica a los PSE de Tipo 3 y 4) da como resultado una duración de impulso de alrededor del 10 por ciento de la que tienen los PSE de Tipo 1 y 2.

La característica de potencia extendida es otro cambio importante. El PD mide la resistencia del cable y calcula la pérdida de potencia y, por lo tanto, la reserva de potencia requerida para garantizar que el PD reciba la potencia de entrada mínima detallada por la especificación. En el peor de los casos, esto equivaldrá a la reserva de potencia especificada por las modificaciones anteriores, pero en aplicaciones prácticas es probable que sea menor, lo que ahorra energía.

Inicio de la PoE de alta potencia

La introducción de cuatro clases adicionales de potencia de salida PSE (Clases 5 a 8) y la correspondiente potencia de entrada PD junto con dos nuevos tipos (Tipos 3 y 4) de PSE y PD han hecho que la secuencia de inicio de la tecnología sea más compleja. Esto tiene implicaciones para los desarrolladores que diseñan sistemas PoE de alta potencia y podría influir en la elección del controlador PSE.

En general, un dispositivo compatible con el IEEE 802.3af o IEEE 802.3at se denomina dispositivo Tipo 1 (Clase 0-3) o Tipo 2 (Clase 4). Los dispositivos que cumplen con el IEEE 802.3bt se conocen como dispositivos Tipo 3 (Clase 5, 6) o Tipo 4 (Clase 7, 8). La PoE de alta potencia define un método para encender de forma segura un PD a través de un cable mediante un PSE y, luego, apagar la alimentación si un PD se desconecta del cable.

El IEEE 802.3bt también presenta una corriente de irrupción y una limitación de tiempo para garantizar la compatibilidad entre PSE y PD de cualquier tipo o clase. El límite de irrupción que es de 400 mA a 450 mA para Clase 0 a 4, 400 mA a 900 mA para Clase 5 a 6, y 800 mA a 900 mA para Clase 7 a 8. El límite de irrupción de PSE se aplica hasta 75 ms después del encendido, después de lo cual el PSE Tipo 2, 3 o 4 admite una corriente de salida más alta de acuerdo con la Clasificación.

El proceso de inicio de PoE de alta potencia comienza cuando el PSE apaga la alimentación mientras observa si se ha enchufado algo al cable. El PSE luego clasifica el PD antes de suministrar la potencia demandada por el PD, o la potencia máxima del PSE si no tiene la capacidad adecuada para abastecer completamente el PD. También hay un cuarto estado operacional utilizado por los PSE Tipo 3 y 4 para verificar si el PD tiene la misma firma de clasificación en cada par trenzado.

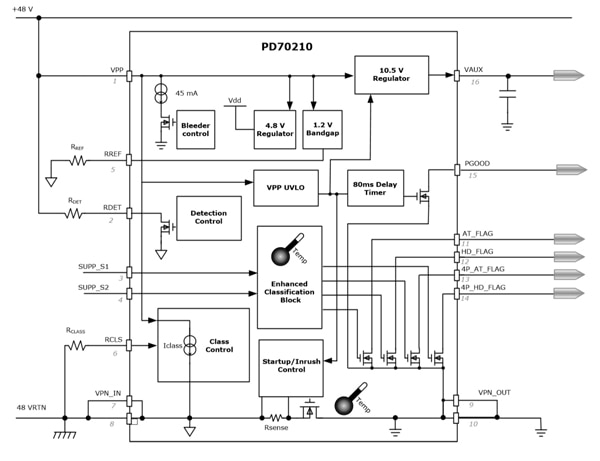

Debido a que es una característica opcional, no todos los PSE y PD compatibles con PoE de alta potencia son compatibles con Autoclass, por lo que se requiere una verificación de la hoja de datos si la funcionalidad forma parte de la especificación del sistema del desarrollador. El controlador de interfaz del PD PD70210ILD-TR de Microsemi es un producto que lo hace a través de su "Bloque de clasificación mejorado". El PD70210ILD-TR también identifica cuál de los cuatro pares del cable recibe energía y genera indicadores apropiados (Figura 1).

Figura 1: El controlador de interfaz de PD PD70210ILD-TR de Microsemi incluye un Bloque de clasificación mejorado para facilitar la clasificación de las nuevas clases y tipos de PD introducidos en la PoE de alta potencia. El chip también puede identificar cuál de los cuatro pares trenzados del cable recibe energía a través de sus pines SUPP_S1 y SUPP_S2. (Fuente de la imagen: Microsemi)

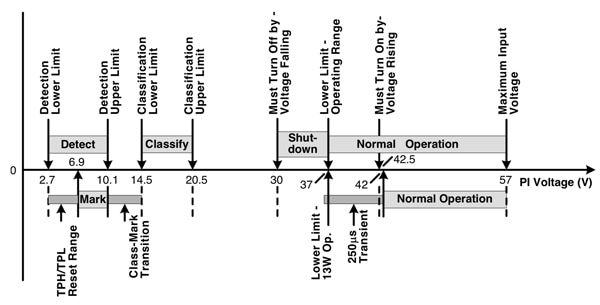

Un PSE que implementa Autoclass primero verifica si el PD es compatible con la función al verificar que la corriente de la Clase caiga al nivel actual de Clase 0 después de un breve retraso. Si hay compatibilidad, el PSE puede proceder a la medición de Autoclass inmediatamente después del encendido, con el PD requerido para obtener su potencia más alta en los siguientes 1.35 a 3.65 segundos. Una vez iniciado, el PD debe presentar un MPS para asegurar al PSE que aún está conectado. La pérdida del MPS activa el PSE para apagar la alimentación (Figura 2).

Figura 2: El proceso de inicio de la PoE de alta potencia es más complejo que las versiones anteriores debido a la introducción de las nuevas clases y tipos de PSE y PD. Aquí se muestran las tres etapas principales del proceso (detección, clasificación y operación) y los voltajes de entrada en los que ocurren. (Fuente de la imagen: Texas Instruments)

Los nuevos controladores cumplen con la especificación de la PoE de alta potencia

Desde la ratificación de la PoE, los desarrolladores se han beneficiado de la disponibilidad de los controladores PSE integrados y las interfaces de PD en las que se basan sus diseños. La tendencia continúa con IEEE 802.3bt. Cortesía de los fabricantes que diseñaron productos para cumplir con la versión de borrador de la especificación, ya hay varios controladores PSE e interfaces PD en el mercado, además del dispositivo Microsemi descrito anteriormente.

Por ejemplo, Linear Technology ofrece el chipset LTC4291-1/LTC4292. Los componentes están diseñados para trabajar juntos para formar controladores PSE de Tipo 3 o 4. La administración de alimentación incluye monitoreo de corriente de 14 bits por puerto, límite de corriente programable y apagado versátil de puertos preseleccionados. La detección de PD utiliza un mecanismo de detección multipunto patentado para ayudar a prevenir una falsa identificación de PD. Autoclass es compatible y el chipset es programable con pin o I2C para negociar hasta 71.3 vatios en el PD.

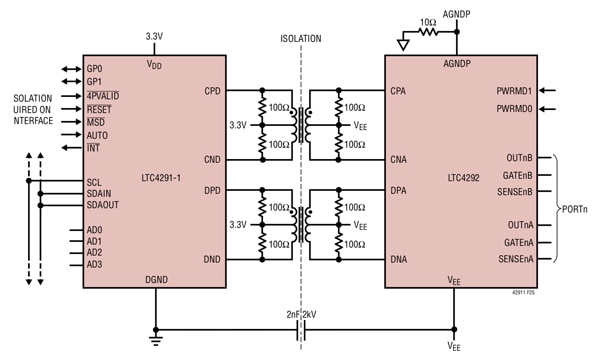

El chipset LTC4291-1/LTC4292 es notable por su nivel de integración; prácticamente todos los circuitos necesarios para implementar un diseño PSE compatible con IEEE 802.3bt se incluyen con solo unos pocos periféricos adicionales requeridos. El dispositivo se divide en dos chips (procesador más fuente de alimentación) para simplificar el aislamiento de PSE, lo que permite que el LTC4291-1 resida en el lado no aislado. Allí puede recibir alimentación de la fuente lógica principal y conectarse directamente al bus I2C/SMBus. El chipset utiliza un esquema de aislamiento patentado para la comunicación de intercambio, que reemplaza los optoacopladores y las fuentes de alimentación aisladas con transformadores de bajo costo. Los transformadores son unidades 10BASE-T o 10/100BASE-T con una relación de revoluciones de 1:1 e inductores de modo común (Figura 3).

Figura 3: El controlador PSE PoE IEEE 802.3bt de cuatro puertos LTC4291-1/LTC4292 de Linear Technology implementa un aislamiento patentado que simplifica el diseño al reemplazar los optoacopladores y las fuentes de alimentación aisladas con transformadores de bajo costo. (Fuente de la imagen: Linear Technology)

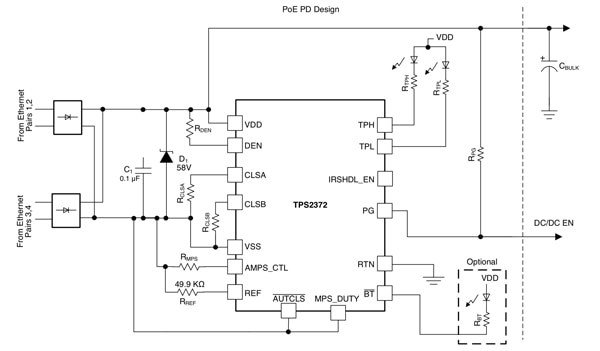

Para aprovechar al máximo el PoE de alta potencia, un PD necesita una interfaz Tipo 3 o 4, de lo contrario, el PSE solo suministrará la potencia máxima definida por IEEE 802.3af de 15.4 vatios (12.95 vatios en el PD). Una opción para esta interfaz es TPS2372-4RGWT de TI, que contiene todas las funciones necesarias para implementar una interfaz de PD IEEE 802.3bt Tipo 1 a Tipo 4.

Una baja resistencia del interruptor interno permite que el TPS2372-3 y el TPS2372-4 admitan aplicaciones PoE de alta potencia de hasta 60 vatios y 90 vatios respectivamente, y su función MPS automática permite aplicaciones que requieren modos de espera de muy baja potencia. Tenga en cuenta que el requisito MPS de IEEE 802.3bt para el PD es aplicable en el extremo de PSE del cable. Eso significa que, dependiendo de la longitud del cable y otros parámetros, incluida la capacitancia a granel, puede requerirse una mayor duración de MPS para verificar. Para ese propósito, el TPS2372 tiene tres selecciones diferentes de duración de pulso MPS y ciclo de trabajo, seleccionables a través de su pin de entrada MPS_DUTY.

El TPS2372 implementa niveles de corriente de irrupción compatibles con todos los tipos de PSE. El chip también implementa una función de retardo para permitir que el PSE complete su fase de irrupción antes de liberar la salida de Buena potencia (PG), asegurando que se cumplan los requisitos de inicio de IEEE 802.3bt. La entrada de habilitación Autoclass del chip proporciona acceso a todos los modos avanzados de optimización de potencia del sistema especificados en el estándar IEEE 802.3bt.

Empezar con la PoE de alta potencia

Cuando se usa un chipset altamente integrado, como el LTC4291-1/LTC4292, el proveedor de silicio ha realizado una gran parte del trabajo de diseño desafiante, pero aún hay algunas pautas de diseño de la placa de CI y selección de componentes externos cuidadosas que deben considerarse. Gran parte de esto sigue las pautas generales de diseño para el diseño del sistema PoE pero con la selección de componentes apropiados para los niveles de voltaje y corriente más altos introducidos por la PoE de alta potencia.

Por ejemplo, se requieren una fuente de alimentación digital y una fuente de alimentación PoE principal para las líneas VDD y VEE que se muestran en la Figura 3. VDD requiere 3.3 voltios y VEE requiere un voltaje negativo de entre -51 y -57 voltios para los PSE de Tipo 3 y de -53 a -57 voltios para los PSE de Tipo 4. Se debe colocar una tapa de desacoplamiento de cerámica de al menos 0.1 μF de VDD a DGND, tan cerca como sea posible de cada LTC4291-1. Para mantener el aislamiento requerido, LTC4292 AGNDP y LTC4291-1 DGND no deben estar conectados.

VEE es la principal fuente aislada de la PoE que proporciona energía a los PD. Debido a que suministra una cantidad relativamente grande de energía y está sujeto a transitorios de corriente significativos, requiere más cuidado de diseño que un simple suministro lógico. Para lograr la mejor eficiencia del sistema, VEE debe ajustarse a una amplitud máxima cercana (57 voltios), dejando un margen suficiente para tener en cuenta el sobreimpulso o el subimpulso transitorio, la deriva de la temperatura y la regulación de la línea. Se requiere un capacitor a granel electrolítico de al menos 47 µF entre AGNDP y VEE para minimizar los reinicios por señal falsa en el caso de transitorios eléctricos.

La selección de un MOSFET externo es otra decisión de diseño clave para el desarrollador. Este MOSFET forma el dispositivo de interruptor de alimentación que controla la salida del PSE. La elección del componente tiene un efecto significativo en la confiabilidad del sistema y requiere que el diseñador analice y pruebe el área operativa segura (SOA) de MOSFET contra las diversas condiciones límite actuales de PSE. Linear Technology recomienda el Nexperia PSMN075-100MSEX para PSE configurado para entregar hasta 51 vatios en el PD, o el PSMN040-100MSEX para 71.3 vatios en el PD porque estos MOSFET han demostrado ser confiables en las aplicaciones de la PoE.

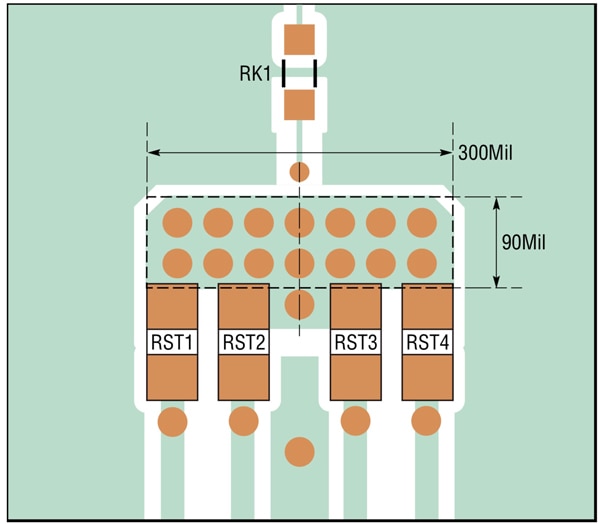

El chipset LTC4291-1/LTC4292 está diseñado para una resistencia de detección de corriente de 0.15 Ω por canal. El desarrollador debe agregar dos resistencias paralelas de 0.3 Ω posicionadas como se muestra en la Figura 4. Las resistencias sensoriales deben tener una tolerancia de ±1 por ciento o mejor, y un coeficiente de temperatura de no más de ±200 partes por millón (ppm)/°centígrados (C) para cumplir con la especificación PoE de alta potencia.

Figura 4: Se muestra el diseño de bloque de resistencia de detección de capa superior e inferior requerido para el LTC4292. La selección y colocación de la resistencia de detección (RSTx) es vital para cumplir con la especificación PoE de alta potencia. (Fuente de la imagen: Linear Technology)

Cada puerto requiere un capacitor de 0.22 μF a través de OUTnA y OUTnB a AGNDP (vea la Figura 3, nuevamente) para mantener el LTC4292 estable mientras está en el límite de corriente durante el inicio o la sobrecarga. Se recomiendan los capacitores cerámicos X7R con capacidad para al menos 100 voltios y deben ubicarse cerca del LTC4292.

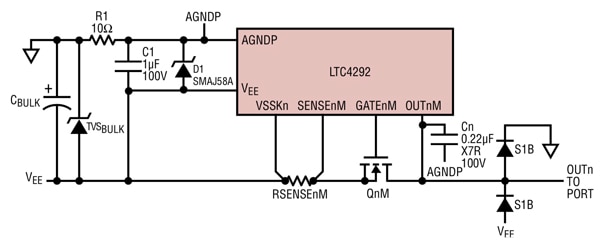

Los puertos Ethernet pueden estar sujetos a transitorios eléctricos significativos. La protección integral de sobretensión para los sistemas PoE es un tema relacionado que requiere un artículo separado, pero un requisito mínimo es un supresor de voltaje volumétrico como un diodo de supresión de voltaje transitorio (TVS) (TVSBULK) y una capacitancia a granel (CBULK) para suprimir la corriente de sobretensión y voltajes a niveles seguros para cada puerto (Figura 5). También se requiere una resistencia en serie de 10 Ω (R1) desde el suministro AGND al pin LTC4292 AGNDP. A través del pin AGNDP LTC4292 y el pin VEE debe haber un diodo TVS de 58 voltios (D1) y un capacitor de derivación (C1) de 1 μF y 100 voltios colocado cerca de los pines LTC4292. Finalmente, cada puerto requiere un par de diodos de sujeción S1B: uno de OUTnM para suministrar AGND y uno de OUTnM para suministrar VEE. Estos son los que dirigen los transitorios eléctricos hacia los rieles de suministro donde son absorbidos por los supresores de sobretensión.

Figura 5: Los controladores PSE requieren protección contra transitorios eléctricos. Aquí se muestra el LTC4292 de Linear Technology con los supresores y componentes de voltaje/corriente necesarios para alejar los transitorios de los chips sensibles. (Fuente de la imagen: Linear Technology)

En la interfaz de PD, el alto nivel de integración para chips como el TPS2327 de TI nuevamente hace la vida un poco más fácil para el desarrollador, pero también se requieren algunos componentes externos (Figura 6).

Por ejemplo, se requieren diodos en la entrada del cable a la interfaz PD. Para el TPS2327, TI recomienda diodos Schottky discretos o de puente de 3 a 5 amperes y calificados a 100 voltios en lugar de diodos convencionales en aplicaciones de PoE de alta potencia porque la disipación de energía en los diodos es un 30 por ciento menor. Una cosa que debe considerar el desarrollador es que los diodos Schottky a menudo tienen una corriente de fuga inversa más alta que los diodos de unión PN normales, lo que dificulta cumplir con el voltaje máximo de retroalimentación de 2.8 voltios definido en la especificación. Para compensar, se deben usar límites de temperatura de funcionamiento de diodo conservadores y dispositivos de baja fuga para esta implementación. Los diodos Schottky también son más susceptibles a los transitorios eléctricos que los diodos convencionales, por lo que se recomienda la protección de voltaje/corriente en forma de perlas de ferrita y capacitores.

La especificación IEEE 802.3bt incluye un capacitor de derivación de entrada de 0.05 a 0.12 μF (típicamente una cerámica de 0.1 μF, 100 voltios, ±10 %) a través de VDD a VSS. La especificación también requiere una resistencia de detección, RDEN, resistencias de clasificación RCLSA y RCLSB, y una resistencia MPS RMPS. Se recomienda una resistencia de 24.9 kΩ, ±1 % para RDEN. Las resistencias de clasificación están conectadas de CLSA y CLSB a VSS para programar la clasificación actual según el estándar IEEE 802.3bt. El valor de estas resistencias y la potencia de clase asignada se determina por la potencia promedio máxima extraída por el PD durante la operación. RMPS establece el ciclo de trabajo MPS; por ejemplo, una resistencia de 1.3 kΩ establece el ciclo de trabajo en 26.4 %. Si se acorta MPS_DUTY a RSS, se establece el ciclo de trabajo en 12.5 %.

La interfaz de PD de la PoE de alta potencia también requiere la supresión del voltaje del diodo TVS y del capacitor de gran volumen (D1, CBULK) a través de las líneas de alimentación para absorber los transitorios eléctricos en este extremo del cable.

Figura 6: El diagrama de la aplicación para la interfaz de PD de la PoE de alta potencia TPS2372 de TI muestra los componentes periféricos necesarios para completar el diseño, principalmente diodos de entrada, dispositivos de supresión, y resistencias MPS, de detección y clasificación. (Fuente de la imagen: Texas Instruments)

Existen muchas pautas de diseño para garantizar que el diseño de la placa de CI, la colocación de piezas y los requisitos de enrutamiento cumplan con los requisitos de la especificación IEEE 802.3bt en términos de precisión de medición paramétrica, robustez del sistema y disipación térmica. Tanto Linear Technology como TI ofrecen diseños de referencia para sus interfaces PSE/PD que se adhieren a las especificaciones y forman una guía útil para el desarrollador.

Conclusión

La PoE de alta potencia extiende las aplicaciones de PoE y mejora la eficiencia. Sin embargo, ha agregado complejidad de implementación a través de la introducción de más controladores PSE y Tipos y Clases de interfaz de PD, así como características operativas y de seguridad adicionales.

Para el diseñador, la ayuda viene en forma del controlador PSE integrado y soluciones de interfaz de PD que incluyen estas características como estándar. Estos simplifican y aceleran enormemente el proceso de diseño al reducir la cantidad de componentes periféricos necesarios para completar el sistema.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.