¿Puede un ADC ser solo un generador de números aleatorios?

2025-10-22

¿Qué tan bueno es un ADC? Esta pregunta no se refiere a cuántos bits de resolución tiene; quizá te sorprenda saber que un ADC de 16 bits no siempre proporciona 16 bits de información útil. "Muchos ADC de 16 bits funcionan realmente como ADC de 7 bits y generadores de números aleatorios de 9 bits", dice Mike Stone en "Choosing an ADC" (Elegir un ADC). Este artículo muestra cómo determinar si un ADC está generando más números aleatorios que útiles, junto con algunas formas sencillas de reducir la aleatoriedad.

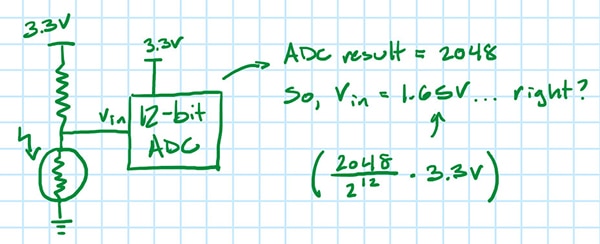

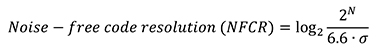

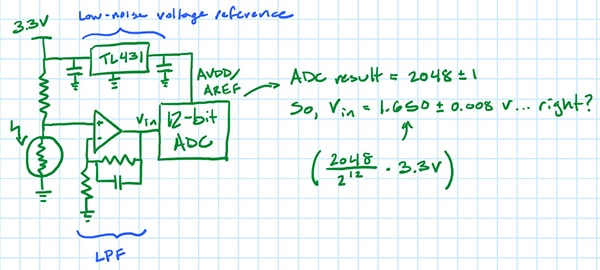

Consideremos una configuración simplificada: un ADC que mide la tensión en una fotorresistencia. Si el ADC de 12 bits de la figura 1 (con VFS = 3.3 V) indica un valor de 2048, ¿significa eso que la tensión en la fotorresistencia es de 1.65 V?

Figura 1: Configuración ADC simplificada para medir el voltaje de una fotorresistencia. (Fuente de la imagen: Nathan Jones)

Figura 1: Configuración ADC simplificada para medir el voltaje de una fotorresistencia. (Fuente de la imagen: Nathan Jones)

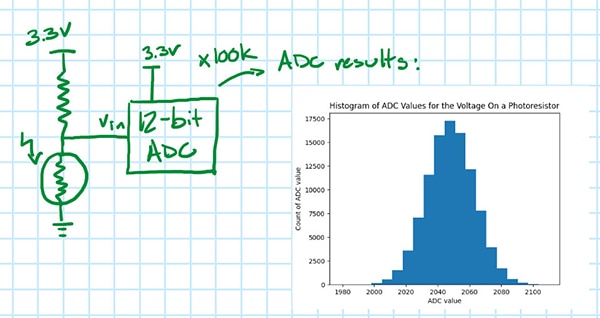

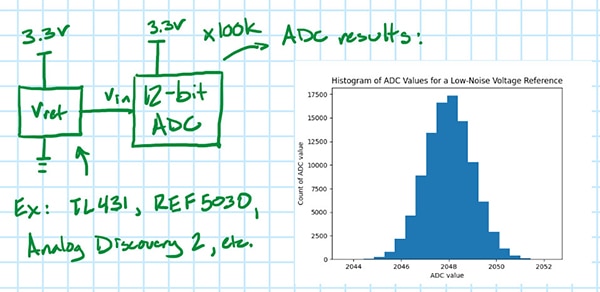

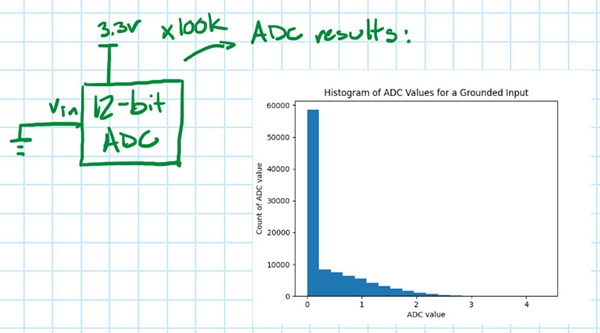

No, en realidad no. Para demostrarlo, tome una segunda muestra, luego una tercera y, de hecho, tome 100,000 muestras y trace los resultados. Lo que se verá es una distribución de valores ADC (Figura 2); si nada ha cambiado en la configuración, entonces cualquiera de ellos podría ser el verdadero voltaje en la fotorresistencia, siendo el candidato más probable el valor medio de todas esas muestras.

Figura 2: El inserto muestra el histograma de valores del ADC para 100,000 muestras de voltaje de la fotorresistencia. (Fuente de la imagen: Nathan Jones)

Figura 2: El inserto muestra el histograma de valores del ADC para 100,000 muestras de voltaje de la fotorresistencia. (Fuente de la imagen: Nathan Jones)

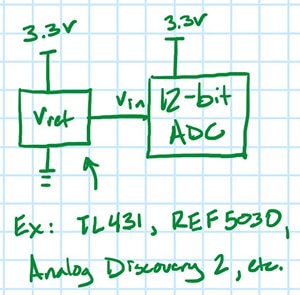

Esto plantea otra cuestión. ¿Podrían ser algunas de esas variaciones reales en la señal de entrada? Sí, podría. Para comprobarlo, se cambiará el divisor resistivo por una referencia de tensión (Figura 3) con un nivel de ruido conocido y se repetirá el experimento.

Figura 3: Nueva configuración de prueba con una referencia de tensión en lugar del divisor resistivo. (Fuente de la imagen: Nathan Jones)

Figura 3: Nueva configuración de prueba con una referencia de tensión en lugar del divisor resistivo. (Fuente de la imagen: Nathan Jones)

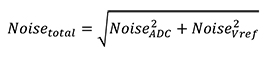

Idealmente, la referencia de tensión utilizada debería tener un nivel de ruido inferior a 1/3 del nivel de ruido esperado en el ADC (por ejemplo, si se espera que el ADC tenga ±1 LSB de ruido [que sería ±0.8 mV utilizando el ADC del ejemplo anterior], entonces lo ideal sería que la referencia de tensión tuviera un nivel de ruido inferior a 0.27 mVpp); si lo tiene, entonces se espera que todo el ruido medido deba proceder del ADC, basándose en el hecho de que el ruido no correlacionado se suma en cuadratura (Ecuación 1).

[1]

[1]

Si NoiseVref=NoiseADC/3 entonces Noisetotal=1.054 × NoiseADC. Esto significaría que la referencia de tensión contribuye con solo 5.4% del ruido total, una cantidad insignificante. Si resulta que la referencia de tensión es más ruidosa que 1/3 del ruido del ADC, solo hay que acordarse de restar su contribución de la desviación estándar medida (véase la ecuación 2).

[2]

[2]

Cómo conocer el nivel de ruido de una fuente de tensión

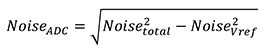

Lo más fácil es encontrarlo en la ficha técnica. Este es un ejemplo de la hoja de datos del REF5030 de Texas Instruments, que muestra que tiene un nivel de ruido de 9 μVpp.

Figura 4: Extracto de la hoja de datos del REF5030 que muestra la especificación de ruido de la tensión de salida. (Fuente de la imagen: Texas Instruments)

Figura 4: Extracto de la hoja de datos del REF5030 que muestra la especificación de ruido de la tensión de salida. (Fuente de la imagen: Texas Instruments)

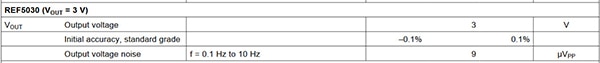

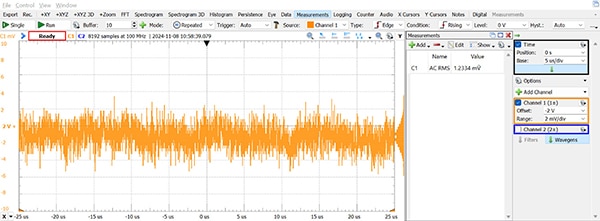

Si en la hoja de datos no se indica el nivel de ruido (o simplemente para verificar su valor), basta con medirlo con un osciloscopio, aunque primero hay que conocer el ruido de fondo del osciloscopio. Esto puede hacerse conectando una de las entradas del osciloscopio a masa y midiendo el valor eficaz de las variaciones de la señal observada. La Figura 5 muestra el resultado de hacer esto con un Analog Discovery 2 (AD2), demostrando que el ruido RMS es de unos 0.9 mV. Curiosamente, este valor disminuye (hasta el rango de µV) si la base de tiempo se incrementa más allá de 8 µs/div, presumiblemente porque el AD2 está utilizando sobremuestreo y decimación para aumentar su resolución efectiva.

Figura 5: Gráfico de nivel de ruido de fondo del osciloscopio Analog Discovery 2. (Fuente de la imagen: Nathan Jones)

Figura 5: Gráfico de nivel de ruido de fondo del osciloscopio Analog Discovery 2. (Fuente de la imagen: Nathan Jones)

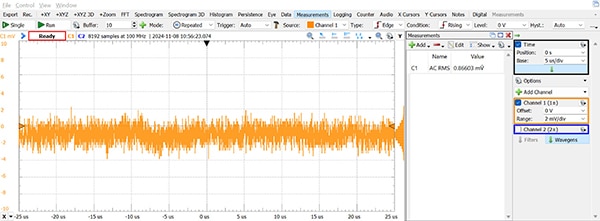

Cuando se mide la fuente de tensión, cualquier variación en la señal del osciloscopio es el resultado del ruido combinado tanto en la fuente de tensión como en el osciloscopio. Siempre que esas fuentes de ruido no estén correlacionadas (lo están), entonces Noisemeasured=√(Noise²Scope+Noise²Vref) y VrefVref=√(Noise²Measured-Noise²Scope), como arriba. Cuando se midió una señal de 2 VCC generada por el AD2, se determinó que el ruido era de 1.2 mV (Figura 6).

Figura 6: Este gráfico de una señal de 2 VCC indica que el ruido del osciloscopio era de 1.2 mV. (Fuente de la imagen: Nathan Jones)

Figura 6: Este gráfico de una señal de 2 VCC indica que el ruido del osciloscopio era de 1.2 mV. (Fuente de la imagen: Nathan Jones)

Esto indicaría que el generador de señal del AD2 también tiene un nivel de ruido de unos 0.9 mV. Esto es lo suficientemente bajo como para probar un ADC de 10 bits (0.9 mV es algo menos de 1/3 de un LSB para un ADC de 10 bits con una lectura a escala completa de 3.3 V); para cualquier ADC de mayor resolución, este ruido tendría que tenerse en cuenta en las mediciones.

Figura 7: El inserto muestra el nuevo histograma de valores del ADC para 100,000 muestras de voltaje de la fotorresistencia con la referencia de voltaje. (Fuente de la imagen: Nathan Jones)

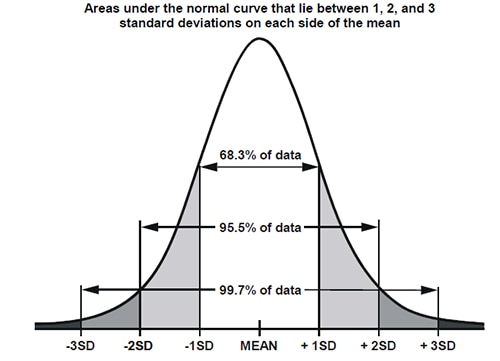

¡Así está mucho mejor! Observe ahora que el segundo histograma (Figura 7) solo llega hasta 2052 en el eje x (la distribución en ese gráfico [Figura 8] tiene una desviación típica de 1 LSB), mientras que el primer gráfico llegaba hasta 2100 (tenía una desviación típica de 15 LSB). Esto se denomina prueba de histograma de CC para un ADC y la desviación estándar indica efectivamente cuánto ruido hay en el ADC: cada vez que se mide un valor con el ADC, solo hay una probabilidad de 68% de que el valor verdadero en el pin analógico esté realmente dentro de ±1 desviación estándar de ese valor, pero hay una probabilidad de 99.7% de que el valor verdadero esté dentro de ±3 desviaciones estándar de ese valor.

Figura 8: Curva de distribución con desviaciones estándar. (Fuente de la imagen: https://i.sstatic.net/jkMDV.png)

Figura 8: Curva de distribución con desviaciones estándar. (Fuente de la imagen: https://i.sstatic.net/jkMDV.png)

Al convertir esta desviación estándar de LSB a voltios se obtiene el ruido referido a la entrada para el ADC (Ecuación 3).

![Input - referred noise [V_RMS ]=(σ∙V_FS)/2^N Ecuación 3](http://sc-c.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2025/October/Can%20an%20ADC%20Be%20Just%20a%20Random%20Number%20Generator/article-2025october-can-an-adc-be-just-equation3.jpg?la=en&ts=6126a5a1-ecae-4e79-bfb0-97e98cce83fa) [3]

[3]

Si el ADC tiene tan poco ruido que todos los códigos ADC caen en un único bin, pruebe a bajar la tensión de referencia del ADC. El nivel de ruido seguirá siendo el mismo, pero ocupará más códigos ADC que antes, lo que permitirá encontrar un valor adecuado para el ruido referido a la entrada.

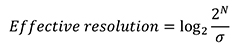

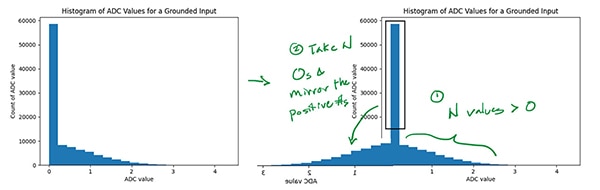

La resolución efectiva y la resolución de código libre de ruido (NFCR) de un ADC representan hasta qué punto este ruido limita la resolución del ADC, que se calcula dividiendo toda la gama de códigos del ADC en intervalos que son solo tan amplios como una (ecuación 4) o 6.6 desviaciones estándar (ecuación 5).

[4]

[4]

[5]

[5]

Básicamente, hay menos bits reales en el resultado porque cada vez hay más posibilidades de que los últimos bits del resultado del ADC sean erróneos o tengan ruido.

Una versión ligeramente más sencilla de la prueba del histograma de CC consiste simplemente en conectar a tierra la entrada del ADC y, a continuación, crear un histograma (Figura 9) de los resultados del ADC, como se hizo con el osciloscopio.

Figura 9: El inserto muestra el histograma de las muestras de tensión de salida del ADC con la entrada conectada a tierra. (Fuente de la imagen: Nathan Jones)

Figura 9: El inserto muestra el histograma de las muestras de tensión de salida del ADC con la entrada conectada a tierra. (Fuente de la imagen: Nathan Jones)

La desviación estándar de este histograma es también una medida del ruido del ADC (menos cualquier contribución del ruido en el voltaje de referencia del ADC, que no afectará a las lecturas de 0 V), pero es optimistamente baja. El ADC probablemente informa de los valores inferiores a 0 V como solo 0, por lo que solo la mitad de la verdadera distribución de ruido se está viendo. En este caso, el ruido del ADC podría aproximarse si se supone que la distribución era simétrica respecto a su valor medio, cambiando suficientes valores de la mediana a números negativos para que la distribución pasara a ser simétrica y calculando a continuación la desviación estándar de la misma (Figura 10).

Figura 10: Reflejo del histograma de la figura 9 para aproximar el ruido del ADC. (Fuente de la imagen: Nathan Jones)

Figura 10: Reflejo del histograma de la figura 9 para aproximar el ruido del ADC. (Fuente de la imagen: Nathan Jones)

Bien, ¿qué se puede hacer con todo este ruido? Si la resolución del ADC sigue cumpliendo los requisitos del proyecto (¡qué suerte!), ten en cuenta que toda medición del ADC conlleva cierta incertidumbre:

- Al comparar dos valores de ADC, considérelos equivalentes solo si están dentro de un margen de 6.6 σ (para tener una confianza del 99.7% en la comparación) o si están dentro de un margen de σ (para tener solo una confianza del 68%).

- Al comparar un valor ADC con un umbral, añada algo de histéresis a la comparación del umbral (como hace un termostato) para evitar que el sistema embebido se vuelva a disparar por encima y por debajo de ese umbral solo en función del ruido.

Si resulta que el ADC ya no cumple los requisitos del proyecto, hay algunas cosas sencillas que se pueden intentar para mejorar su rendimiento. En cuanto al hardware, se incluyen:

- Utilizar una referencia de bajo ruido (como el REF5030 de Texas Instruments o el TL431 de EVVO) para AVCC y AREF.

- Garantizar una diafonía mínima entre las señales analógicas y digitales en la placa de circuito impreso.

- Apagado de la CPU durante las conversiones ADC (si la MCU lo admite), para reducir el ruido digital.

En cuanto al software, la señal de entrada puede sobremuestrearse (es decir, tomar la media de N muestras) para reducir el ruido, aunque esto reducirá claramente la frecuencia de muestreo máxima. (De hecho, se podría utilizar una técnica llamada "sobremuestreo y decimación" para aumentar la resolución del ADC en una cantidad relacionada con el número de veces que se sobremuestrea la entrada).

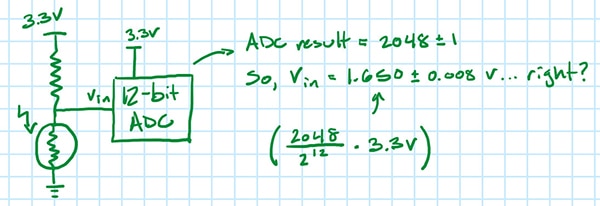

Supongamos que la desviación estándar de una prueba de histograma de CC para la configuración inicial es de 1 LSB. Si el ADC lee 2048, ¿ahora significa eso (hay una probabilidad de 68% ) que el valor verdadero es 1.650±0.008 V (Figura 11)?

Figura 11: Suponiendo que la desviación estándar de la configuración de la Figura 1 es 1 LSB y la salida del ADC es 2048, ¿es la tensión de entrada real 1.650±0.008 V? (Fuente de la imagen: Nathan Jones)

Figura 11: Suponiendo que la desviación estándar de la configuración de la Figura 1 es 1 LSB y la salida del ADC es 2048, ¿es la tensión de entrada real 1.650±0.008 V? (Fuente de la imagen: Nathan Jones)

¡Más cerca, pero aún no! Esto se debe a que todos los ADC tienen dificultades para medir una señal de entrada que cambia rápidamente a cierta frecuencia, lo que da lugar a mediciones imprecisas (es decir, ruido). Sorprendentemente, la frecuencia a la que esto ocurre puede estar muy por debajo de la frecuencia de muestreo máxima del ADC. Esto significa que un ADC de 12 bits con una frecuencia de muestreo de 1 MSPS (megamuestras por segundo) puede no tener realmente 12 bits de resolución para señales de entrada cercanas a 500 kHz; la resolución de ese ADC puede caer a 6 bits o menos cuando la frecuencia de la señal de entrada es tan alta. Si se intenta medir una señal en la fotorresistencia superior a 10 Hz, es posible que el ADC no tenga 12 bits de resolución.

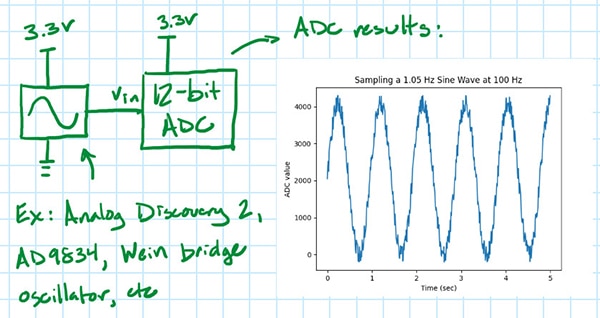

Para determinar el grado de resolución del ADC con frecuencias de entrada más altas, envíe una señal conocida (esta vez, una onda sinusoidal) y mida en qué medida los valores del ADC coinciden con la señal conocida (Figura 12). (¿Es la onda sinusoidal "suficientemente buena"? Eso se discutirá después de revelar el procedimiento para realizar la prueba; así tendrá más sentido).

Figura 12: Configuración de prueba con una entrada de onda sinusoidal conocida. (Fuente de la imagen: Nathan Jones)

Figura 12: Configuración de prueba con una entrada de onda sinusoidal conocida. (Fuente de la imagen: Nathan Jones)

Para la onda sinusoidal, se puede utilizar un generador de funciones (como los que se encuentran en muchos osciloscopios USB), un chip DDS (como el AD9834 de Analog Devices), o se puede montar un generador de onda sinusoidal personalizado (basado en un oscilador de puente de Wien o utilizando un MAX7400 de Analog Devices para filtrar paso bajo una onda cuadrada, por ejemplo). Es importante tener en cuenta que para esta prueba solo deben utilizarse frecuencias de entrada que no sean submúltiplos enteros de la frecuencia de muestreo (por ejemplo, no utilice una frecuencia de entrada de 1 kHz si la frecuencia de muestreo es de 100 kHz). Esto es para evitar el muestreo erróneo de la onda sinusoidal en los mismos lugares en cada ciclo. Además, para forzar al máximo el ADC, ajuste la amplitud de la onda sinusoidal de entrada al mayor valor que no "recorte" la salida (por ejemplo, algo ligeramente inferior a 1.65 V para el ADC de los ejemplos anteriores).

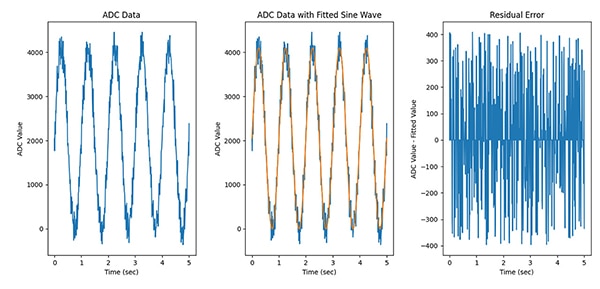

Tras recoger los resultados del ADC, los datos se ajustan a una onda sinusoidal para calcular el error residual. El ajuste de la onda sinusoidal puede realizarse con casi cualquier cantidad de datos, pero para obtener los mejores resultados, tiene que haber al menos cinco periodos completos de la onda sinusoidal de entrada. Es probable que el algoritmo de ajuste sinusoidal tenga que ser inicializado dándole conjeturas iniciales para la amplitud, la frecuencia, el desplazamiento de fase y el desplazamiento (Figura 13).

Figura 13: Utilizando un algoritmo de ajuste de ondas sinusoidales, puede determinarse el error residual. (Fuente de la imagen: Nathan Jones)

Figura 13: Utilizando un algoritmo de ajuste de ondas sinusoidales, puede determinarse el error residual. (Fuente de la imagen: Nathan Jones)

Esta prueba se denomina prueba de ajuste de onda sinusoidal para un ADC, y el valor RMS del error residual es una medida de lo ruidoso que es el ADC a esa frecuencia de entrada específica. A frecuencias más bajas, el ruido RMS debería coincidir con el ruido referido a la entrada de la prueba del histograma de CC, pero a frecuencias más altas es casi seguro que se degradará como resultado de las fuentes de ruido dependientes de la frecuencia mencionadas anteriormente.

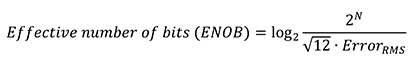

El valor de ruido RMS de la prueba de ajuste de la onda sinusoidal puede utilizarse para calcular el número efectivo de bits (ENOB) del ADC (Ecuación 6), que es el número de bits de un ADC ideal cuya única fuente de ruido, el ruido de cuantificación, tiene el mismo valor RMS que el ruido del ADC.

[6]

[6]

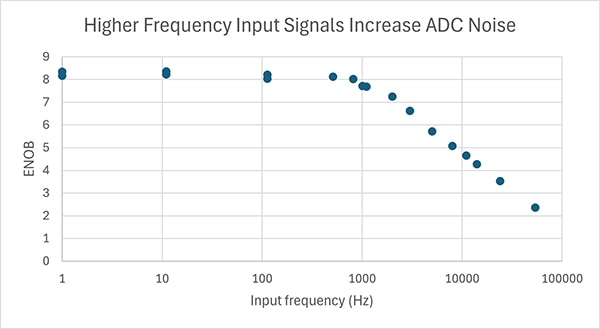

Este valor es específico de la frecuencia de la señal de entrada utilizada. Para obtener una imagen más completa del ADC, esta prueba debe repetirse a frecuencias hasta la señal de entrada más alta de interés, o hasta la mitad de la frecuencia de muestreo máxima. Es posible que el ruido aumente (¡y el ENOB disminuya!) a frecuencias muy por debajo de la mitad de la frecuencia de muestreo máxima. Por ejemplo, se realizó esa misma serie de pruebas en el ADC de un STM32F042K6 de STMicroelectronics y se trazaron los resultados (Figura 14).

Figura 14: Prueba de ruido de frecuencia para un ADC en un microcontrolador STM32F042K6. (Fuente de la imagen: Nathan Jones)

Figura 14: Prueba de ruido de frecuencia para un ADC en un microcontrolador STM32F042K6. (Fuente de la imagen: Nathan Jones)

Aunque el ADC del microcontrolador STM32F042K6 puede muestrear a 1 MHz, la resolución disminuye por encima de 1 kHz; si la intención fuera medir una señal de 10 kHz con este ADC, ¡solo habría unos 5 bits de resolución en ese punto! (Obsérvese también que el ENOB máximo es de unos 8.3; esto se debe a ~10 LSB de ruido incluso con CC, que reducen la resolución efectiva del ADC de 12 bits a unos 8.7 bits de golpe. Estas pruebas se realizaron en una placa de desarrollo Nucleo-F042 de STMicroelectronics sin modificar; los resultados serían mucho mejores si se utilizara alguna de las técnicas mencionadas anteriormente ["Vale, ¿qué se puede hacer con todo este ruido?"]).

Cómo saber el nivel de ruido de una onda sinusoidal

Al igual que con la referencia de tensión, si el nivel de ruido de la onda sinusoidal es a priori (es decir, si no está disponible en una hoja de datos), entonces es necesario medirlo con un osciloscopio. El uso de la técnica de ajuste de onda sinusoidal comentada anteriormente puede caracterizar el ruido del generador de onda sinusoidal.

- En primer lugar, determine el ruido de fondo del osciloscopio conectando su entrada a tierra y calculando el valor eficaz de la salida (como se ha descrito anteriormente en la sección "Cómo conocer el nivel de ruido de una fuente de tensión").

- A continuación, mide la salida del generador de ondas sinusoidales, ajusta los resultados a una onda sinusoidal perfecta y calcula el valor eficaz de los residuos. A continuación, utilice la ecuación 2 para determinar el ruido del generador de ondas sinusoidales (utilizando el ruido de fondo del osciloscopio como aproximación de su ruido de CA).

- Asegurarse de que la impedancia de salida del dispositivo conectado al pin analógico es muy baja, posiblemente insertando un op-amp para amortiguar.

- Ajustar el reloj del ADC o su tiempo de muestreo/retención para que sea lo más rápido posible, sin dejar de dar al capacitor interno tiempo suficiente para cargarse.

- Utilizar una fuente de reloj ADC de baja fluctuación y configurar el sistema para que tome muestras ADC a intervalos regulares.

- Caracterización del ADC Raspberry Pi Pico

- Comprender los convertidores de datos (Texas Instruments)

- Comprender SINAD, ENOB, SNR, THD, THD + N y SFDR para no perderse en el ruido de fondo (Analog Devices)

- Lo bueno, lo malo y lo feo del ruido de entrada de los ADC: ¿no hay ruido que valga? (Analog Devices)

- Cómo aprovechar al máximo el ADC del SAM D21 (Códigos Thea)

- "Pruebas de convertidores analógico-digitales" (Kent Lundberg)

- Pruebas dinámicas del rendimiento del convertidor A/D (Texas Instruments)

- Cómo optimizar la precisión del ADC en las MCU STM32 (STM)

- Aumento de la resolución ADC mediante sobremuestreo (Atmel)

- Fundamentos del análisis del ruido de los ADC de precisión (Texas Instruments)

- Calibración de errores de ganancia y compensación de ADC en MCU basados en ARM® Cortex-M0®+ (Microchip)

- Generación de onda sinusoidal mediante filtrado de paso bajo de una onda cuadrada

- Comprender el impacto del ruido del digitalizador en las mediciones del osciloscopio (EE Times)

- Número efectivo de bits (diseño robusto de circuitos)

Idealmente, el nivel de ruido de la onda sinusoidal es inferior a 1/3 del nivel de ruido esperado del ADC (en otras palabras, la onda sinusoidal es "espectralmente pura"), lo que haría que su contribución al ruido medido fuera insignificante. Si el nivel de ruido de la onda sinusoidal es superior, no olvide restarlo del ruido medido obtenido al calcular los valores eficaces del error residual.

Esta prueba debe repetirse para cada frecuencia de entrada que se vaya a utilizar para probar el ADC (¡incluso el generador de ondas sinusoidales puede tener fuentes de ruido dependientes de la frecuencia!)

¿Qué se puede hacer con todo este ruido? En primer lugar, se recomienda poner un filtro de paso bajo (LPF) entre la fuente de señal y el ADC, con una frecuencia de corte justo por encima de la señal más alta de interés, para ayudar a limitar el ruido de alta frecuencia (esto es una "buena cosa que hacer", en general, para cualquier sistema de adquisición de datos). Si la señal de frecuencia más alta de interés está por debajo de la "rodilla" en el gráfico de ENOB frente a la frecuencia de entrada, entonces realmente no hay ninguna pérdida de resolución. Cuando se trata de medir señales por encima de esa "rodilla", hay algunas cosas que se pueden intentar para mejorar esa resolución a frecuencias más altas. Entre ellos se incluyen:

A menos que el objetivo sea una señal en una banda muy estrecha de frecuencias, lo más sencillo es suponer que las señales de entrada reales tienen el mismo contenido de frecuencia desde CC hasta la frecuencia de corte del LPF y, por lo tanto, que el ruido RMS en cada medición del ADC es el ruido RMS medio medido utilizando la prueba de ajuste de onda sinusoidal desde CC hasta la frecuencia de corte. Si se desea medir señales de banda ancha de hasta 10 kHz utilizando el STM32F042K6 comentado anteriormente, entonces lo mejor sería operar como si el ADC solo tuviera un ENOB de unos 6 bits para cada medida. Este valor puede muy bien ser inferior al determinado mediante la prueba del histograma de CC, lo que indica que hay menos certeza en cada una de las mediciones del ADC si existe la posibilidad de que tengan un mayor contenido de frecuencia.

La siguiente suposición a considerar es la adición de un LPF entre el sensor y el ADC de tal forma que el ruido RMS desde DC hasta la frecuencia de corte sea de solo ±1 LSB. Si el ADC lee 2048, ¿ahora significa eso (hay una probabilidad de 68%) que el valor verdadero es 1.650 ±0.008 V (Figura 15)?

Figura 15: ¿La adición de un filtro de paso bajo en el circuito da como resultado un valor verdadero de 1.650±0.008 V? (Fuente de la imagen: Nathan Jones)

Figura 15: ¿La adición de un filtro de paso bajo en el circuito da como resultado un valor verdadero de 1.650±0.008 V? (Fuente de la imagen: Nathan Jones)

Aunque parezca una locura, ¡todavía no! Aunque este artículo ha caracterizado eficazmente el ruido del ADC, aún no ha caracterizado su error. Tras las pruebas aquí descritas, solo se puede confiar en que dos valores del CAD sean iguales o diferentes. Sin embargo, se desconoce si un código ADC de 2048 corresponde exactamente a 1.65 V o a otra cosa. Los errores de ganancia, offset y no linealidad diferencial (entre otros) podrían significar que la conversión de un código ADC a un voltaje real es más complicada que usar Vin=resultado ADC × VFS/2N. Pero eso es tema para otro artículo.

Referencias

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.