Tutorial sobre ADC/DAC

Colaboración de DigiKey

2017-09-13

Hoy el mundo está plagado de señales digitales y analógicas. Si bien estas señales se comportan de manera diferente, a menudo se utilizan para ayudar a lograr un objetivo mayor. Imagine al ingeniero encargado de controlar una unidad HVAC. Si planea usar cualquier tipo de microprocesador o microcontrolador, será necesario poder leer una temperatura analógica que tenga una cantidad infinita de valores y convertir esto en una representación binaria establecida en pasos discretos. Esta representación binaria del valor analógico será procesada por el microcontrolador o microprocesador. Estos datos se utilizarán para ayudar a ejecutar un proceso por la unidad HVAC para ayudar a mantener un entorno estable. Cuando se trata de un valor analógico que necesita ser procesado por un sistema digital, es imperativo contar con un convertidor analógico-digital (ADC). El mismo principio puede aplicarse al revés a una señal digital que necesita ser convertida en una señal analógica. Reproducir una canción online implica varios pasos que utilizan la conversión de señales digitales a señales analógicas. La señal que recibe el dispositivo host del servidor será una representación binaria de la señal analógica original. La respuesta audible de estos datos binarios serían ininteligibles para el oyente. La señal original era analógica entonces la representación final también tendrá que ser analógicas. Este problema se resuelve mediante el uso del convertidor de digital a analógico (DAC). Este tipo de dispositivos tiene un código binario que podría haber sido codificados mediante un conversor de analógico a digital, y volverse nuevamente a una tensión analógica.

Convertir señales de analógico a digital o digital a analógico es una tarea ineludible para el ingeniero de hoy. Hay muchos tipos diferentes de convertidores de analógico a digital y digital a analógico. Si bien estos difieren en cuanto a su arquitectura, todos ellos trabajan para alcanzar un mismo fin. El procesamiento de la señal digital ya que no se puede hacer con los valores analógicos, sería similar a una persona de habla francesa tratando de hablar con una persona de habla alemana. No funcionaría sin un traductor. Los dispositivos ADC y DAC pueden ayudar a actuar como traductor. Cuando un ADC observa una tensión analógica, su trabajo es convertir la tensión analógica en un código binario en un determinado período de tiempo. Esto significa que el ADC realiza una muestra de la tensión analógica en un instante, y luego determina cuál sería el valor en binario en el lado de salida del ADC. La cantidad de muestras que el dispositivo toma cada segundo será mencionada en su documentación. Un ejemplo de esto sería el MAX1118EKA+T de Maxim Integrated. Este dispositivo tiene una velocidad de muestreo de 100 kHz para que pueda probar la tensión analógica en su lado de entrada 100.000 veces por segundo. Al ser capaz de tomar muchas muestras en un segundo, es posible registrar con precisión cómo se vería la tensión analógica mediante una interpretación binaria. A veces la tasa de muestreo de un ADC no es lo suficientemente alta para recrear con precisión su entrada lo cual provoca un solapamiento. Aquí es donde las señales comienzan a ser indistinguibles unas de las otras, o en solapamiento unas de otras. Imagine una cámara de video que puede tomar 24 fotogramas por segundo durante la grabación. Para la mayoría de las aplicaciones esto estará bien; sin embargo, si intenta ver algo que se mueve muy rápido, esto puede distorsionar la imagen. Recuerde el efecto de ver la televisión en una grabación de finales de la década de los noventa. La imagen de la televisión tenía parpadeo. Esto es porque la tasa de actualización en la televisión en sí es mucho más rápida que lo que la grabación puede capturar en su tasa dada de fotogramas por segundo. La imagen se vería distorsionada debido a que el video es en realidad una sucesión de imágenes. Más cosas ocurren entre cada imagen que lo que está efectivamente representado en el video. El mismo tipo de efecto puede ocurrir con un ADC. Para evitar esto, es pertinente asegurarse de que la frecuencia de muestreo sea por lo menos dos veces mayor que la frecuencia más alta que se debe transmitir. Esto se conoce como la tasa de Nyquist.

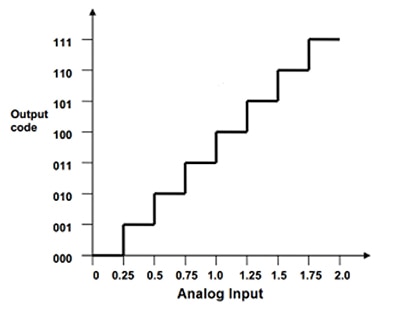

Tener una mayor tasa de muestreo permitirá al dispositivo ser más preciso, pero esta no es la única manera de controlar la precisión. Dado que se trata de convertir una señal analógica en un código binario, habrá un número finito de pasos discretos que se puedan utilizar para representar la tensión en un punto en el tiempo. El número de bits que se pueden utilizar para representar este número es la resolución. Cuanto mayor sea la resolución de la ADC, más discretos serán los pasos que pueden ser adoptados por ella. Para más detalle, esto es importante para entender cómo determinar cuántos pasos puede hacer un ADC. Un ADC tiene una salida binaria que es representativa de la tensión de alimentación. Si la tensión de alimentación es de 10 V y hay un ADC de 8 bits, entonces existe una posibilidad de 256 pasos. Para determinar la resolución utilice la ecuación 2n. El "2" es una constante y N es el número de bits que hay. Al tomar 28 terminamos con 256 pasos. Utilizando 256 pasos con una alimentación de 10 V significa que cada paso será de 39.0625 mV. Habrá un código binario diferente para cada uno de estos pasos. Si se tuvieran que explorar todas las posibles opciones de entrada en un ADC comenzando desde la más bajo a la más alta, se vería el perfil de una escalera. Esta escalera es la función de transferencia del ADC. La figura 1 ilustra la transferencia mediante un ADC de 3 bits con una referencia de 2 V.

Figura 1: Función de transferencia de un ADC de 3 bits con 2 V de referencia. (Cortesía de Microchip Technology)

Puesto que hay tres bits, es posible calcular el número total de pasos utilizando la ecuación 2n como sigue:

![]()

Como es evidente en la Figura 1, hay ocho pasos entre el 000 y el 111. Cada paso escala un LSB.

Como se mencionó anteriormente, existen diferentes tipos de arquitecturas ADC. Los tres arquitecturas ADC más populares son registros de aproximaciones sucesivas (SAR), Delta-Sigma (∆∑) y convertidores de canalización. Cada uno de estos va a convertir una señal analógica en una salida digital, pero existen ligeras diferencias en cómo se hace esto. El SAR hará una muestra de entrada analógica y la mantiene, para convertirla en una señal digital y, a continuación, pasarla. Los convertidores Delta-Sigma hacen un promedio de la muestra durante el tiempo que se tarda para convertirla en una señal digital. Los convertidores de canalización dividen la conversión en diferentes etapas para permitir velocidades de conversión muy rápidas. Cada uno de estos tendrá aspectos positivos y negativos. La arquitectura SAR será fácil de usar, normalmente utiliza menos energía, y tiene tiempo de latencia baja con alta precisión. La arquitectura Sigma-Delta tendrá una resolución muy alta y alta estabilidad a baja potencia y bajo costo; sin embargo, funcionará a velocidades mucho menores que la SAR y las arquitecturas de canalización. El ADC de canalización funcionará en las velocidades más altas y mayor ancho de banda que los ejemplos anteriores, pero tendrá una menor resolución y requiere más energía para funcionar.

Registros de aproximaciones sucesivas.

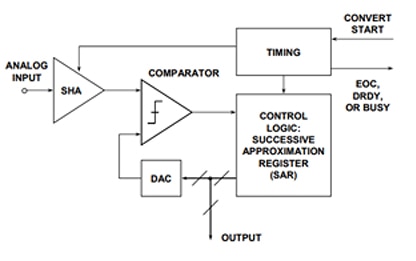

Los registros de aproximación sucesiva son los tipos más populares de ADC. A menudo tendrán una interfaz SPI o I2C, pero a veces habrá una salida paralela. Para ayudar a procesar la señal analógica de SAR, los ADC tendrán un muestreo y retención para intentar mantener la señal constante. Hay un comparador que mide la entrada analógica contra un DAC interno. Este DAC se ajustará a ½ de su potencial de tensión en este punto. Si la entrada es mayor que el DAC, el comparador de salida tendrá ua salida de 1 a ser almacenada en el MSB en el "registro de aproximaciones sucesivas". Después de esto el DAC se ajustará a ¼ de su potencial de voltaje y el proceso se repite. El siguiente valor para el DAC sería de 1/8, 1/16 y así sucesivamente hasta que todos los bits se hayan cargado en el registro. Hay una analogía que ayuda a ilustrar esto, que implica sucesivamente la adición o no adición de pesos para ver cuánto es el peso de algo más. La figura 2 ilustra este punto.

Figura 2: Analogía ilustrativa de cómo un ADC de aproximación sucesiva obtiene un valor digital desde un valor analógico. (Cortesía de Analog Devices)

El bloque = 45 unidades, la primera prueba es utilizar 32 pequeños bloques cada uno es una unidad de 1. El bloque es todavía más pesado que los bloques más pequeños. Ya que el bloque es todavía la más pesado, los bloques más pequeños permanecerán. La siguiente prueba es para agregar 16 bloques más pequeños. Esto sería de 32 + 16 lo cual equivale a 48, por lo tanto, es demasiado pesado. Como resultado de ser demasiado pesado, los 16 bloques se descartan. La siguiente prueba es para añadir 8 bloques más a la escala, ya que 32 + 8 será igual a 40, cantidad que será agregada. Desde allí es posible agregar 4 bloques más resultando en 44 bloques. Después de que dos bloques adicionales sean añadidos, pero esto resultará en 46 unidades que es mayor de 45 entonces los bloques son removidos. Finalmente se añade un bloque para que el peso de los bloques sea igual en ambos lados. Cada vez que se agregan los bloques, el número agregado se reduce a la mitad. Esto es representativo del valor determinado desde la DAC a la SAR. La figura 3 muestra un diagrama de bloques de un ADC de registro de aproximación sucesiva.

Figura 3: diagrama de bloques funcionales de ADC de aproximación sucesiva (Cortesía de Analog Devices)

Un ejemplo de un ADC SAR es el ADS7886SDBVT de Texas Instruments. Este es un ADC de 12 bits, lo que significa que puede tomar 4.096 pasos entre 0 V y la tensión de alimentación. La tasa de muestreo es de 1 MHz, lo que significa que este aspecto en su entrada un millón de veces por segundo. Ya que el rendimiento de ADC debe ser probado antes de ser implementado en un producto acabado, a menudo los fabricantes hacen una herramienta de evaluación para ayudar a probar. El ADS7886SDBVT tiene una herramienta de evaluación, es el ADS7886EVM. Esto hace que las pruebas sean mucho más fáciles porque ya hay una placa establecida con todos los componentes pasivos que serán necesarios para efectuar pruebas funcionales de la ADC.

Sigma Delta ∆∑

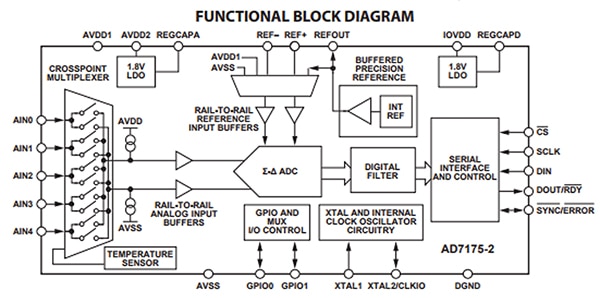

Los convertidores Sigma Delta son muy populares para cualquier cosa que necesite alta resolución y precisión. La grabación de audio sería un buen ejemplo de una aplicación para un convertidor Delta Sigma. Los convertidores Sigma Delta necesitan sobremuestreo de sus entradas. La tasa de Nyquist no es tan relevante cuando hablamos de convertidores Sigma Delta, que trabajarán de manera óptima cuando la tasa de muestreo es aproximadamente 20 veces superior a la máxima frecuencia a muestrear. La salida del convertidor Delta Sigma se introduce en un filtro digital y decimador que procesa el flujo de bits para producir la salida final. A menudo habrá una interfaz serial entre el filtro y la salida digital. Un ejemplo de un ADC Delta Sigma sería el AD7175-2BRUZ de Analog Devices, Inc. En la figura 4 se muestra el diagrama de bloques funcionales del AD7175-2BRUZ.

Figura 4: Diagrama de bloques funcionales de ADC Sigma-Delta de Analog Devices. (Cortesía de Analog Devices)

Este ADC Sigma Delta tiene una resolución de 24 bits y una velocidad de muestreo de 250 kHz. Esto tendrá un potencial de hasta 16.777.216 pasos. Esto significa que hay una resolución mucho más alta que en el ejemplo anterior; sin embargo, alrededor de 1/4 de la frecuencia de muestreo. Como en el ejemplo anterior, el AD7175-2BRUZ también tiene una placa de evaluación para fines de prueba. Esta placa es la EVAL-AD7175-2SDZ y proporciona una manera sencilla de evaluar el ADC.

Canalización

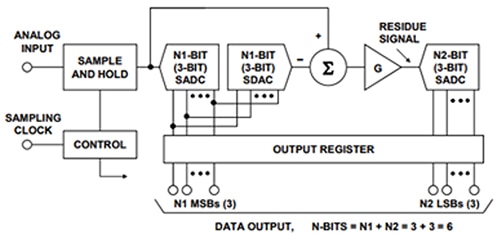

Los ADC de canalización son los más rápidos. Un ejemplo de "Arquitecturas ADC V: ADC de subrango de canalización" que ayuda a ilustrar esto usando un ADC de canalización de 6 bits. El muestreo y retención es como el SAR, pero directamente después del muestreo y retención habrá convertidor falsh sub-ADC de 3 bits que digitaliza la señal. La conversión de 3 bits será para los 3 bits más significativos. Esto se convierte a una señal analógica mediante un sub-DAC. Esta salida se restará de la salida de muestreo y retención, amplificada, y luego se vuelve a enviar al sub-ADC de segunda fase de 3 bits para los restantes tres bits menos significativos. La figura 5 es un diagrama de bloques que ilustra este punto.

Figura 5: Diagrama de bloques funcionales de ADC de sugrango de canalización. (Cortesía de Analog Devices)

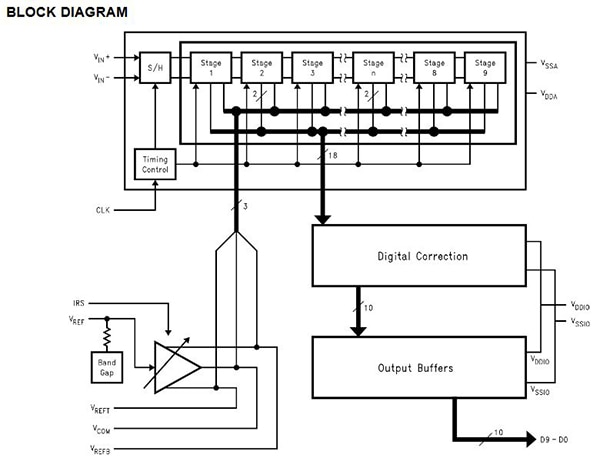

Un ejemplo de un ADC de canalización sería el ADC10080CIMT/NOPB de Texas Instruments. Este es un ADC de 10 bits, por lo que tiene un potencial de 1.024 pasos y puede convertir 80 Megamuestras por segundo. Las aplicaciones para este dispositivo serían el ultrasonido y la imagen, instrumentación, sistemas de adquisición de datos, o cualquier cosa que implique una conversión rápida. Mirando el diagrama de bloques del ADC10080CIMT/NOPB, uno puede ver que está configurado como se describe anteriormente. La figura 6 tiene el diagrama de bloques tomados de la hoja de datos del ADC1008CIMT/NOPB.

Figura 6: Diagrama de bloques funcionales ADC10080CIMT/NOPB de Texas Instruments (Cortesía de Texas Instruments)

DAC ponderado binario

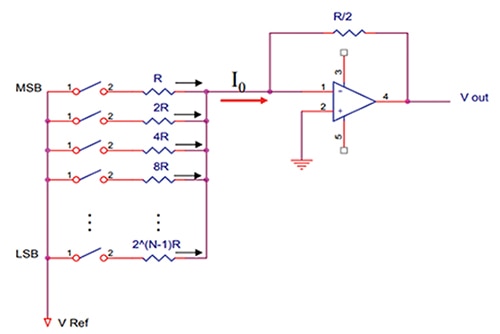

Hasta este punto, este artículo se ha centrado en el lado de ADC de la conversión de los datos, pero esto es sólo la mitad de la batalla. A menudo es necesario convertir datos binarios en una señal analógica. Aquí es donde encontramos el convertidor de digital a analógico. A menudo el primer tipo de CAD que se enseña en la escuela es el DAC ponderado binario. Esto implica el uso de un sistema de resistencias cuyo salidas se reúnen en la misma suma de resistencia. Los bits más significativos emiten más corriente que los bits menos significativos. Esto se hace creando una red resistiva inversamente proporcional. Dado que cada bit binario del código digital tendrá el mismo valor de tensión, mediante resistencias inversamente proporcionales en cada bit, mientras mayor bits permitirá que más corriente fluya a través de ellos. Este método particular de conversión no es muy popular debido a la facilidad de métodos utilizados hoy en día; sin embargo, es un muy buen punto de partida para describir cómo funcionan los DAC. La mayor dificultad con este método es encontrar resistencias de distinto nivel que funcionen juntas. La tolerancia tendría que ser increíblemente ajustada y es más fácil buscar varias resistencias de calor similar que de valores diferentes como el que usa el método ponderado binario. La figura 7 ilustra esta arquitectura mediante un esquema de una red de resistencia ponderada binaria.

Figura 7: Representación esquemática de una red de registro ponderado binario (Cortesía del Georgia Institute of Technology)

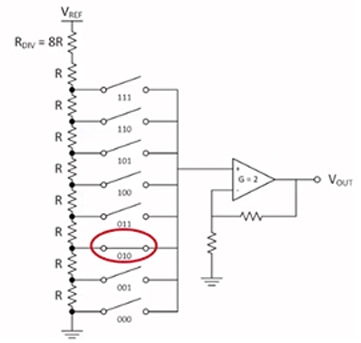

DAC en cadena

Otra arquitectura popular de DAC es la cadena DAC. Esta es la arquitectura más simple, pero también menos lineal, y a veces se denomina divisor de Kelvin. Esto tiene una cadena de resistencias en serie de igual valor. La cadena tendrá una tensión de referencia en la parte superior, una impedancia alta resistencia antes de la cadena, y cada nodo tendrá un interruptor que está dedicado a un código binario que se cerrará cuando el código es leído por el dispositivo. Esto permite usar un valor de voltaje analógico, lo cual depende de la entrada binaria. La figura 8 proviene de un video titulado "¿Qué es una cadena CAD?" de Texas Instruments. Se elige el código 010 para el valor decimal de 2. El interruptor en 010 está ahora cerrado permitiendo que el voltaje de CC en ese nodo se pase al amplificador sumador.

Figura 8: Representación esquemática de cadena CAD (Cortesía de Texas Instruments)

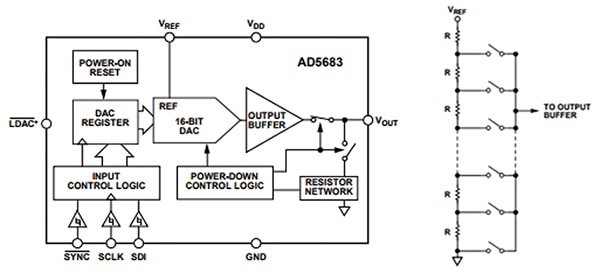

Los DAC en cadena son fáciles de producir, porque utilizan el mismo valor de resistencia para cada parte de la cadena (menos la resistencia de alta impedancia). Un ejemplo de un DAC en cadena sería el AD5683RBRMZ de Analog Devices Inc. Es un DAC en cadena de 16 bits que trabaja con SPI. La figura 9 muestra un diagrama de bloque funcional de este dispositivo y la figura 10 muestra el divisor resistivo. Este producto también tiene una herramienta de evaluación, la EVAL-AD5683RSDZ

Figuras 9 y 10: Diagrama de bloques funcionales AD5683RBRMZ de Analog Devices (izquierda) y su red de divisores de resistencia (derecha). (Cortesía de Analog Devices)

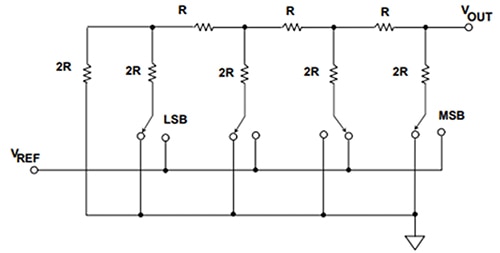

R-2R

La red R-2R es una arquitectura DAC muy común. Esto utiliza sólo dos valores de resistencias, sus valores no importan tanto mientras 2R sea dos veces tan grande como R. Esto hace que los DAC R-2R sean muy escalables. Independientemente de cuántos bits sea el DAC, seguirá habiendo sólo necesidad de dos valores de resistencias. La figura 11 muestra una red de escalera de R-2R red de 4 bits.

Figura 11: Representación esquemática de un DAC R-2R. (Cortesía de Analog Devices)

Esta red divisor utiliza el teorema de Thevenin para finalmente obtener la resistencia equivalente de Thevenin para toda la red de "R". Cada etapa permitirá el doble de la tensión que la última etapa. En este ejemplo, si el Vref era de 5 V, entonces mientras más alejada esté la fase izquierda de LSB, sólo sería capaz de producir 0.3125 V. Moviéndose de izquierda a derecha, la tensión de salida proporcional sería:

![]()

Esto es representativo de todas las entradas digitales, X0 es el LSB y X3 es el MSB. Utilizando una referencia de 5 V nos daría:

![]()

Por la misma lógica, para encontrar cuál sería la tensión analógica para el bit más significativo sería posible tomar las siguientes:

![]()

Si hay una entrada binaria de 1111, la salida no sería igual a 5 V. Recordar el debate sobre la resolución anterior. Si hay un DAC de 4 bits, entonces puede haber 16 pasos. Esto es debido a que 24 permitiría 16 pasos. El LSB está a 0.3125 V, si uno tuviera que multiplicar 0.3125 x 16 se llegaría a 5 para obtener una respuesta. Esto es engañoso porque uno de los pasos supondrá un avance de 0 V para representar 0000 binario. Esto significa que la máxima tensión que puede conseguirse es la tensión de alimentación menos el voltaje LSB. Esto nos deja con 4.6875 V.

![]()

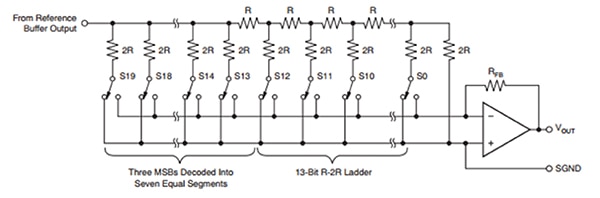

Un ejemplo de una DAC R-2R sería el DAC8734SPFB de Texas Instruments. Esto es un convertidor de 16 bits que ejemplifica cómo estos dispositivos son escalables. El diseño utilizado para el R-2R en esta red es muy similar a lo descrito anteriormente. La figura 12 muestra la red R-2R para el DAC8734SPFB. También hay una herramienta de evaluaciófv;n para el DAC8734SPFB, el DAC8734EVM.

Figura 12: Representación esquemática de DAC DAC SPFB8734R-2R de Texas Instruments (Cortesía de Texas Instruments)

Hay muchos otros tipos de arquitecturas ADC/DAC, pero en este artículo sólo hemos cubierto algunas de las arquitecturas más populares. Estos dispositivos son necesarios en el mundo actual de procesamiento de señal digital. Sin dispositivos ADC/DAC no sería posible integrar una salida analógica en cualquier tipo de procesamiento de señal digital o viceversa. Es fácil para la persona común en la materia a darlo por sentado, pero para el ingeniero encargado de conectar componentes analógicos hasta un sistema digital, este es uno de los pasos más importantes que hay que considerar. Cuando piense en la tecnología analógica a la digital, hay que recordar la analogía de las dos personas que hablan distintos idiomas. Si esas personas no tienen un traductor que no serían capaces de comunicarse unos con otros. Sin utilizar adecuadamente los dispositivos ADC/DAC, un dispositivo tendría que usar estrictamente digital o estricatemente analógico. Los dispositivos ADC/DAC son un gran apretón de manos entre ambos mundos.

Recursos

- “AVR127: Entender los parámetros ADC”. Mayo. 2016.

- "Elegir el convertidor A/D adecuado para su aplicación". Recuperado el 8 de mayo. 2017.

- Kester, Walt. “Arquitecturas ADC II: ADC de aproximación sucesiva”. Octubre de 2008.

- Kester, Walt. “Arquitecturas ADC III: Fundamentos de ADC Sigma-Delta”. Octubre de 2008.

- Kester, Walt. “Arquitecturas ADC IV: ADC Sigma-Delta conceptos avanzados y aplicaciones”. Octubre de 2008.

- Kester, Walt. “Arquitecturas ADC V: ADC de subrango de canalización” Oct. 2008.

- Kester, Walt. "Fundamentos de la interfaz DAC". Octubre de 2008.

- Kester, Walt. “Arquitecturas DAC básicas II: DAC bonarios”. Octubre de 2008.

- Lee, J. K. Jeelani, Beckwith, J. "Conversor de digital a analógico". Recuperado el 8 de mayo. 2017

- Poole, Matt. "¿Qué es un DAC en cadena?". 4 de abril, 2016

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.